ПРЕОБРАЗОВАТЕЛИ КОДОВ

Преобразователь кодов описывается системой логических уравнений, где аргументами являются элементы преобразуемого кода, а функцией – каждый элемент преобразованного.

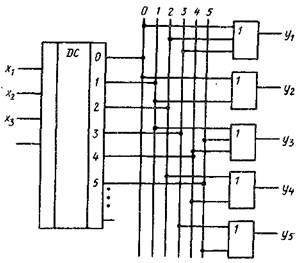

Выполнение преобразователя кода на дешифраторе и шифраторе покажем на примере реализации табл. 7.1. Принцип преобразования состоит в том, что каждая комбинация входного, а также выходного кодов рассматривается как двоичное число, а преобразователь – как преобразователь чисел. При этом каждому входному коду-числу – дешифратор ставит в соответствие возбужденный выход, которому шифратор должен поставить в соответствие число – выходной код.

Рис. 7.1. Схема преобразователя кодов

| Набор комбинации | Код | |||||||

| преобразуемый | преобразованный | |||||||

| х1 | х2 | х3 | у5 | у4 | у3 | у2 | у1 | |

Исходя из этого составлена схема преобразователя кодов (рис. 7.1), в которой каждый выход дешифратора является входом шифратора, а выполненные соединения отвечают табл. 7.1. Так, число 011 на входе (комбинация №3) возбуждает выход 3 дешифратора, которому шифратор ставит в соответствие число 10001. Аналогично выполнены и другие соединения.

Условное изображение преобразователя кодов приведено на рис. 7.2.

Рис. 7.2. Условное изображение преобразователя кодов

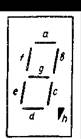

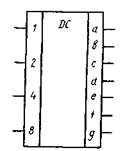

Семисегментный дешифратор. Результаты измерений и вычислений, представленные в двоичном коде, должны индицироваться в привычном для человека десятичном счислении. Для этого двоичный код преобразуют вначале в двоично-десятичный, а затем каждую тетраду последнего отражают на семисегментном индикаторе (рис. 7.3) десятичной цифрой.

Будем считать, что свечение сегмента соответствует логической 1. Тогда справедливы соотношения между видом тетрады и сигналами на индикаторе, приведенные в табл. 7.2. Так, для изображения на индикаторе десятичной цифры 2 (двоичный код 0010) должны светиться сегменты а, b, d, е, g, для изображения 510 – сегменты а, с, d, f, g, что легко установить по рис. 7.3.

Рис. 7.3. Семисегментный индикатор

| Десятичная цифра | Разряды тетрады | Состояние сегментов индикатора | |||||||||

| х4 | х3 | х2 | х1 | a | b | c | d | e | f | g | |

Рис. 7.4. Условное изображение семисегментного индикатора

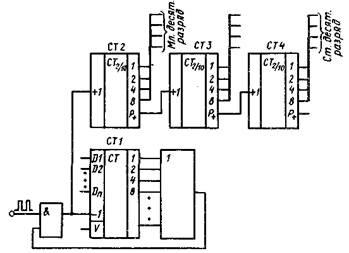

На рис. 7.5 изображена схема устройства, реализующего другой принцип. В двоичный счетчик СТ1 занесено число, представленное на его выходах D1-Dn двоичным кодом, которое должно быть преобразовано в двоично-десятичное. Каждый счетный импульс одновременно уменьшает содержимое счетчика СТ1 и увеличивает на единицу содержимое десятичного счетчика СТ2. После поступления на вход десятичного счетчика каждых десяти импульсов он обнуляется и единица с выхода переноса Р+ записывается в следующий счетчик. Когда счетчик СТ1 обнулится, на выходе элемента ИЛИ окажется логический 0, который заблокирует элемент И, прерывая поступление счетных импульсов ко всем счетчикам. При этом двоичное число из счетчика СТ1 представлено двоично-десятичным в счетчиках СТ2-СТ4. Каждый цикл преобразования начинается с подачи на вход V импульса, разрешающего запись числа с входов D1-Dn в счетчик СТ1. Оно поступает на выходы счетчика и при наличии единицы хотя бы в одном разряде разблокирует элемент И.

Рис. 7.5. Преобразователь двоичного кода в двоично-десятичный

Изложенный принцип получения двоично-десятичного кода может быть реализован еще в процессе формирования двоичного кода, например при аналого-цифровом преобразовании. В этом случае счетные импульсы с выхода ковьгон-ктора должны одновременно поступать на счетчик АЦП и на двоично-десятичные счетчики.

ЦИФРОВАЯ ИНДИКАЦИЯ

ЦИФРОВАЯ ИНДИКАЦИЯ

В зависимости от того, как работает в схеме индикатор (непрерывно или периодически), различают соответственно статический и динамический типы индикации.

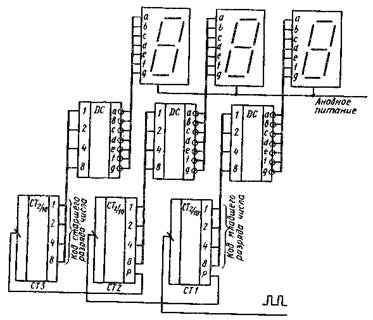

Статическая индикация иллюстрируется рис. 7.6. В десятичных счетчиках СТ1-СТ3 сосредоточены три разряда двоично-десятичного кода. С выхода каждого счетчика двоичный код десятичного разряда возбуждает соответствующие выходы семисегментного дешифратора, в результате чего на индкаторе высвечивается та или иная цифра.

Используемые в схеме индикаторы имеют общий анод, поэтому на возбужденных выходах семисегментных дешифраторов должны присутствовать нули.

Для индикации каждой десятичной цифры необходимы отдельный семисегментный дешифратор и 11 соединительных проводников.

Рис. 7.6. Статическая индикация

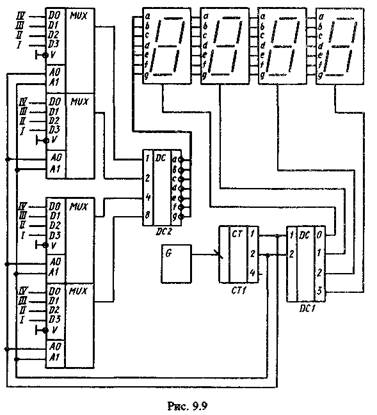

Динамическая индикация состоит в том, что индикаторы работают не одновременно, а по очереди, периодически. Это позволяет иметь в схеме только один семисегментный дешифратор, а каждый его выход соединить с входами одноименных сегментов всех индикаторов: выход а – с входами а, выход b – с входами b и т.д. На время работы каждого индикатора к семисегментному дешифратору должен подключаться тот счетчик, число в котором высвечивает данный индикатор.

Схема рис. 7.7 реализует описанный принцип на примере индикации четырехразрядного десятичного числа. Четыре выхода счетчика IV, содержащего четвертый разряд числа, соединяются с входами D0 четырех мультиплексоров (по два мультиплексора в каждом корпусе). Четыре выхода счетчика III, содержащего третий разряд числа, соединяются с входами D1 мультиплексоров и т.д. (на рис. 7.7 это отражено цифрами IV, III, II, I на соответствующих входах мультиплексоров). За счет общих адресных линий на выходы мультиплексоров одновременно будет поступать информация с одноименных входов: с четырех входов D0 (со счетчика IV разряда), с четырех входов D1 (со счетчика III разряда) и т.д.

Рис. 7.7. Динамическая индикация

В каждый момент времени на дешифраторы в структурах мультиплексоров и на дешифратор DС1 поступает один и тот же код с выходов счетчика СТ1. Поэтому поступление на дешифратор DС2 кода старшего разряда числа с входов D0 (при А0=0, А1=0) будет сочетаться с возбуждением выхода 0 дешифратора DС1, соединенного с анодом левого по схеме индикатора (на котором и должен высвечиваться этот разряд), т.е. с вводом его в работу.

При непрерывной работе генератора G код на выходах счетчика СТ1 будет циклически изменяться: возрастать, принимать нулевое значение, вновь увеличиваться и т.д. Поэтому аналогично описанному будет функционировать каждый индикатор, включаемый при поступлении на анод напряжения логической 1 с соответствующего выхода дешифратора DС1. При частоте возбуждения индикатора порядка 100 Гц его мелькания не ощущаются.

Легко заметить, что число входов каждого мультиплексора должно быть равно числу индикаторов, фиксирующих десятичное число, т.е. числу его разрядов.

Динамическую индикацию выгодно использовать, когда число индицируемых разрядов составляет шесть и более.

| <== предыдущая лекция | | | следующая лекция ==> |

| МЕХАНИЗМ СПРОСА И ПРЕДЛОЖЕНИЯ. РЫНОЧНОЕ РАВНОВЕСИЕ | | | Геологический круговорот воды. |

Дата добавления: 2020-02-05; просмотров: 1124;