Тактируемые регистры

Принцип действия регистров, срабатывающих по фронту тактового сигнала, ничем не отличается от принципа действия D-триггера.

По положительному фронту тактового сигнала С каждый из выходов регистра устанавливается в тот уровень, который был в этот момент на соответствующем данному выходу входе D, и сохраняется таковым до прихода следующего положительного фронта сигнала С. То есть если триггер запоминает один сигнал (один двоичный разряд, один бит), то регистр запоминает сразу несколько (4, 6, 8, 16) сигналов (несколько разрядов, битов). Память регистра сохраняется до момента выключения питания схемы.

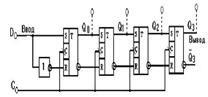

На Рис.4.11. представлена схема регистра на D триггерах, в котором данные в прямом коде подаются на входы D1,D … Dm.

Запись информации осуществляется фронтом сигнала Тзап (тактовый командный импульс) одновременно поступающего на входы С всех триггеров.

|

| Рис.4.11. Запись информации параллельным кодом |

На Рис.4.12. представлена схема регистра на JK триггерах. В данной схеме данные подаются парафазным кодом (прямой код D1,D … Dm – на вход J, обратный кода – на вход К).

|

| Рис.4.12. Запись информации парафазным кодом |

Изменение хранящейся информации в регистре памяти (запись новой информации) осуществляется после установки на входах D0 . . . Dm новой цифровой комбинации (информации) при поступлении определенного уровня (регистр на асинхронных триггерах или запись осуществляется по установочным входам триггера) или фронта синхросигнала (синхроимпульса) Тзап=С на вход «С» регистра (синхронные триггера с записью по информационным входам).

Количество разрядов записываемой цифровой информации определяется разрядностью регистра, а разрядность регистра, в свою очередь, определяется количеством триггеров, образующих этот регистр.

В качестве разрядных триггеров регистра памяти используются синхронизируемые уровнем или фронтом триггеры.

Наращивание разрядности регистров памяти достигается добавлением нужного числа триггеров, тактовые входы которых присоединяют к шине синхронизации.

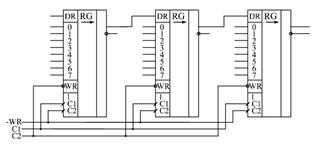

В стандартные серии входит несколько типов параллельных регистров, срабатывающих по фронту (Рис. 4.12).

Рис.4.12. Параллельные регистры стандартных серий, срабатывающие по фронту

Различаются они количеством разрядов, наличием или отсутствием инверсных выходов, наличием или отсутствием входа сброса (–R) или разрешения записи (–WE), а также типом выходных каскадов (2С или 3С) и, соответственно, наличием или отсутствием входа разрешения –EZ. Иногда на схемах тактовый вход С обозначается WR - сигнал записи в регистр.

В качестве примеров в табл. 4.3 приведена таблица истинности регистра ИР27, а в табл. 4.4 - регистра ИР37. По переходу тактового сигнала С из 0 в 1 (положительный фронт) оба регистра записывают в себя входную информацию.

| Таблица 4.3 Таблица истинности регистра ИР27 | Таблица 4.4 Таблица истинности регистра ИР37 | ||||||||

| Входы | Выходы | Входы | Выходы | ||||||

| -WE | C | D | Q | -EZ | C | D | Q | ||

| 0→1 | 0→1 | ||||||||

| 0→1 | 0→1 | ||||||||

| Х | Не меняется | X | Не меняется | ||||||

| Х | Не меняется | X | Не меняется | ||||||

| Х | Х | Не меняется | X | X | Z |

Все регистры, имеющие выход с тремя состояниями, обеспечивают повышенную нагрузочную способность. Задержка переключения регистров примерно соответствует задержке переключения триггеров.

Одно из основных применений регистров состоит в хранении требуемого кода в течение нужного времени.

Регистры могут также применяться в составе вычислителей, выполняя функцию накопителя результата вычисления.

Рассмотрим пример схемы такого вычислителя – накапливающий сумматор..

В самом названии схемы отражена ее функция: она суммирует и накапливает результат. Накапливающий сумматор (Рис. 4.13) состоит из сумматора и выходного регистра, охваченных обратной связью.

То есть на один вход сумматора подается код с выходов регистра, а на другой вход - входной код. В результате с каждым следующим фронтом тактового сигнала в регистр записывается код суммы входного кода с предыдущим содержимым регистра, с

Рис. 4.13. Структура накапливающего сумматора

предыдущей суммой. Например, если входной код равен 3, а в регистре записан код 6, то в следующем такте в регистр будет записан код 9 (то есть 6 + 3), в следующем такте - код 12 (то есть 9 + 3) и т.д. Получается, что на выходе накапливающего сумматора формируется равномерно увеличивающийся двоичный код, и шаг этого увеличения можно менять. В данном случае удобно применять регистр со сбросом, например, ИР35.

Регистры сдвига

Регистры сдвига или сдвиговые регистры (англ. shift register) представляют собой, последовательно соединенную цепочку триггеров.

Т.е. в сдвиговых регистрах все триггеры соединены в последовательную цепочку (выход каждого предыдущего триггера соединен со входом D следующего триггера). Тактовые входы всех триггеров (С) объединены между собой. В результате такой триггер может рассматриваться как линия задержки, входной сигнал которой последовательно перезаписывается из триггера в триггер по фронту тактового сигнала С. Информационные входы и выходы триггеров могут быть выведены наружу, а могут и не выводиться - в зависимости от функции, выполняемой регистром.

Основной режим их работы - это сдвиг разрядов кода, записанного в эти триггеры, То есть по тактовому сигналу содержимое каждого предыдущего триггера переписывается в следующий по порядку в цепочке триггер. Код, хранящийся в регистре, с каждым тактом сдвигается на один разряд в сторону старших разрядов или в сторону младших разрядов, что и дало название регистрам данного типа.

На схемах символом регистра служат буквы RG. Для регистров сдвига указывается также направление сдвига:

· → вправо (основной режим, который есть у всех сдвиговых регистров);

· ← влево (этот режим есть только у некоторых, реверсивных сдвиговых регистров);

· ↔ реверсивный (двунаправленный), т. е. записанную информацию можно сдвигать по линейке триггеров вправо или влево. Для включения режима сдвига предусматривают специальный управляющий вход.

Направление сдвига отражают внутреннюю структуру регистров сдвига (Рис. 4.14) и перезапись сигналов последовательно по цепочке триггеров. При этом триггеры, вполне естественно, нумеруются слева направо, например, от 0 до 7 (или от 1 до 8) для 8-разрядных регистров. В результате сдвиг информации регистром вправо представляет собой сдвиг в сторону разрядов, имеющих большие номера, а сдвиг информации регистром влево - это сдвиг в сторону разрядов, имеющих меньшие номера.

Однако, как известно, в любом двоичном числе слева расположены старшие разряды, а справа - младшие разряды. Поэтому сдвиг двоичного числа вправо будет сдвигом в сторону младших разрядов, а сдвиг влево - сдвигом в сторону старших разрядов. О такой особенности необходимо помнить разработчику цифрового прибора.

Рис. 4.14. Направление сдвига в сдвиговых регистрах

Регистры сдвига могут выполнять функции хранения и преобразования информации.

Они могут быть использованы для построения умножителей и делителей чисел двоичной системы счисления, т.к. сдвиг двоичного числа влево на один разряд соответствует умножению его на два, а сдвиг вправо - делению на два.

Регистры сдвига широко используются для выполнения различных временных преобразований цифровой информации: последовательное накопление последовательной цифровой информации с последующей одновременной выдачей (преобразование последовательной цифровой информации в параллельный код) или одновременный прием (параллельный прием) информации с последующей последовательной выдачей (преобразование параллельного кода в последовательный).

Регистры сдвига могут служить также в качестве элементов задержки сигнала, представленного в цифровой форме: регистры с последовательным приемом (вводом) и выводом осуществляют задержку передачи информации на m+1 тактов (m+1 - число разрядов регистра) машинного времени.

Регистры сдвига чаще все6го реализуются на D-триггерах (Рис.4.15, а) или на RS-триггерах (Рис.4.15, б), где для ввода информации в первый разряд включается инвертор (первый разряд представляет собой D-триггер).

Следует отметить, что все регистры сдвига строятся на базе двухступенчатых триггеров или синхронизируемых фронтом синхроимпульса.

Регистры сдвига могут быть построены и на триггерах одноступенчатой структуры. В этом случае в каждом разряде регистра нужно использовать два триггера, которые управляются двумя сдвинутыми во времени тактовыми импульсами. Если бы в регистре были применены одноступенчатые триггеры по одному на разряд, то правило работы регистра было бы нарушено: при первом же импульсе сдвига информация, записавшись в первый разряд, перешла бы во второй, затем в третий и т.д.

Разрядность регистров сдвига, как и у регистров хранения, определяется количеством триггеров, входящих в их состав.

Работу регистра сдвига рассмотрим на примере схемы, приведенной на Рис. Рис.4.15.

Можно предположить, что в начале все триггеры регистра находятся в состоянии логического нуля, т.е. Q0=0, Q1=0, Q2=0, Q3=0. Если на входе D-триггера Т1 имеет место логический 0, то поступление синхроимпульсов на входы «С» триггеров не меняет их состояния.

Как следует из Рис.4.15, синхроимпульсы поступают на соответствующие входы всех триггеров регистра одновременно и записывают в них то, что имеет место на их информационных входах. На информационных входах триггеров Т2, Т3, Т4 - уровни логического «0», т.к. информационные входы последующих триггеров соединены с выходами предыдущих триггеров, находящихся в состоянии логического «0», а на вход «D» первого триггера, по условию примера, подается «0» из внешнего источника информации.

При подаче на вход «D» первого триггера «1», с приходом первого синхроимпульса, в этот триггер запишется «1», а в остальные триггеры - «0», т.к. к моменту поступления фронта синхроимпульса на выходе триггера Т1 «ещё» присутствовал логический «0». Таким образом, в триггер Т1 записывается та информация (тот бит), которая была на его входе «D» в момент поступления фронта синхроимпульса и т.д.

При поступлении второго синхроимпульса логическая «1» , с выхода первого триггера, запишется во второй триггер, и в результате происходит сдвиг первоначально записанной «1» с триггера Т1 в триггер Т2, из триггера Т2 в триггер Т3 и т.д.. Таким образом, производится последовательный сдвиг поступающей на вход регистра информации (в последовательном коде) на один разряд вправо в каждом такте синхроимпульсов.

После поступления m синхроимпульсов регистр оказывается полностью заполненным разрядами числа, вводимого через последовательный ввод «D».

В течение следующих четырех синхроимпульсов производится последовательный поразрядный вывод из регистра записанного числа, после чего регистр оказывается полностью очищенным (регистр окажется полностью очищенным только при условии подачи на его вход уровня «0» в режиме вывода записанного числа).

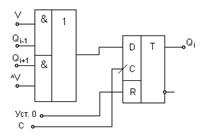

Реверсивные регистры сдвига объединяют в себе свойства регистров прямого и обратного сдвига.

|

|

| а) | б) |

|

|

| в) | г) |

| Рис.4.15. Регистры сдвига и диаграммы работы на D-триггерах (а,б) и на RS-триггере (в,г) |

Рис. 4.16. Разряд реверсивного регистра

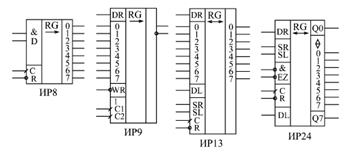

В стандартные серии цифровых микросхем входит несколько типов сдвиговых регистров, отличающихся возможными режимами работы, режимами записи, чтения и сдвига, а также типом выходных каскадов (2С или 3С).

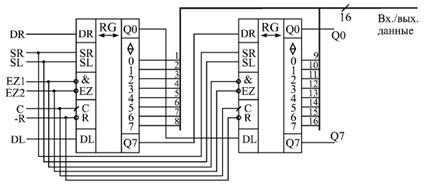

На Рис. 4.17 представлены микросхемы регистров сдвига.

Рис. 4.17. Сдвиговые регистры

Регистр ИР8 - наиболее простой из регистров сдвига. Он представляет собой 8-разрядную линию задержки, то есть имеет только один информационный вход, на который подается последовательная сдвигаемая информация (точнее, два входа, объединенных по функции 2И), и восемь параллельных выходов.

Сдвиг в сторону выходов со старшими номерами осуществляется по переднему фронту тактового сигнала С. Имеется также вход сброса –R, по нулевому сигналу на котором все выходы регистра сбрасываются в нуль.

На рисунке 4.17 представлен пример увеличения разрядности регистра на примере ИС ИР9.

Регистр ИР24 имеет двунаправленную параллельную шину данных. То есть одни и те же выводы микросхемы используются как для параллельной записи информации в регистр, так и для параллельного чтения информации из регистра. При этом двунаправленные выводы данных имеют повышенную нагрузочную способность. Это позволяет легко сопрягать ИР24 с многоразрядными микросхемами памяти и с двунаправленными буферами.

Регистр ИР24 обеспечивает сдвиг информации в обоих направлениях. Имеются входы расширения DR и DL, а также выходы расширения Q0 и Q7, что позволяет легко наращивать разрядность.

Отличие выходов Q0 и Q7 от нулевого и седьмого разрядов данных состоит в том, что Q0 и Q7 - однонаправленные, то есть в

Рис. 4.17. Соединение регистров ИР9 для увеличения разрядности

любом режиме работы выдают информацию с выходов внутренних триггеров младшего и старшего разрядов.

Тактируется регистр положительным фронтом сигнала С.

Предусмотрен сброс регистра нулевым сигналом на входе –R.

Режим работы микросхемы определяется сигналами на управляющих входах SR и SL.

При единичном сигнале на SR и нулевом сигнале на SL по положительному фронту сигнала С происходит сдвиг информации вправо (в сторону разрядов с большими номерами). Запись в разряд 0 производится при этом со входа расширения DR.

При единичном сигнале на SL и нулевом сигнале на SR по положительному фронту сигнала С происходит сдвиг информации влево (в сторону разрядов с меньшими номерами). Запись в разряд 7 производится при этом со входа расширения DL.

При обоих нулях на входах SR и SL регистр переходит в режим хранения. Во всех этих случаях разряды данных работают как вход или как выход в зависимости от сигналов –EZ.

При обеих единицах на входах SR и SL по положительному фронту С в регистр записывается параллельный код, причем разряды данных переходят в состояние приема независимо от сигналов –EZ.

Таблица истинности регистра ИР24 приведена в табл. 4.8.

Объединяя два регистра ИР24, легко получить 16-разрядный сдвиговый регистр с сохранением всех возможностей одной микросхемы (Рис. 4.18).

| Таблица 4.8 Таблица истинности регистра сдвига ИР24 | ||||

| Выходы | Функция | |||

| С | -R | SR | SL | |

| Х | Х | Х | Сброс | |

| 0→1 | Сдвиг вправо | |||

| 0→1 | Сдвиг влево | |||

| 0→1 | Параллельная запись | |||

| Х | Хранение |

Рис. 4.18. Объединение регистров ИР24 для увеличения разрядности

Главное применение всех регистров сдвига состоит в преобразовании параллельного кода в последовательный, и наоборот.

Дата добавления: 2021-12-14; просмотров: 510;