Язык описания аппаратуры AHDL

(Бродин Б.В., Калинин А.В. Системы на микроконтроллерах и СБИС программируемой логики. М.: Изд. ЭКОМ, 2002г., 2000с.)

В России широкое распространение получили программируемые логические схемы

3.2.1.

Оператор оценивает значение выражения и по нему выбирает режим работы схемы в соответствии со списком.

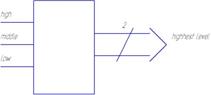

Рассмотрим реализацию логики оператора if на AHDL. В качестве примера возьмем кодировщик приоритета, который преобразует уровень самого приоритетного активного входа в его значение.

SUBDESIGN priority

{low, middle, high: INPUT;

highest_level [1..0]: OUTPUT;

}

BEGIN

IF high THEN

highest_level [ ]=3;

ELSIF middle THEN

highest_level [ ]=2;

ELSIF low THEN

highest_level [ ]=1;

ELSE

highest_level [ ]=0;

END IF

END.

На выходе схемы получается код, соответствующий приоритету того входа, на который подана логическая единица. Если ни один вход не равен 1, то схема выдает 0.

Логическая операция CASE.

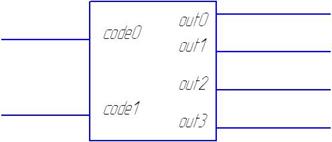

Рассмотрим пример, реализующий функцию дешифратора, преобразующего код из двухразрядного в четырехразрядный.

SUBDESIGN decoder

{code[1..0]: INPUT;

out[3..0] :OUTPUT;

}

BEGIN

CASE code [ ] IS

WHEN 0 => OUT[ ]=B”0001”;

WHEN 1 => OUT[ ]=B”0010”;

WHEN 2 => OUT[ ]=B”0100”;

WHEN 3 => OUT[ ]=B”1000”;

END CASE

END.

С помощью операторов IF и CASE можно проектировать дешифраторы. Однако схема сгенерирования компилятором устройства получается весьма сложной. Поэтому в AHDL введены специальные функции, описывающие дешифратор. Для описания дешифраторов используется объявление таблиц истинности TABLE.

Рассмотрим пример, реализующий дешифратор двоичного кода в сигнал семисегментного индикатора.

SUBDESIGN 7segment

{i[3..0]: INPUT;

Дата добавления: 2022-05-27; просмотров: 233;