Устройство адресации буквенно-цифровых телевизионных СОИ

Устройство адресации в знаковых СОИ формирует адрес знака, определяющий его положение на информационном поле. В телевизионных СОИ адрес знака на информационном поле соответствует адресу ячейки памяти БЗУ, где хранится код этого знака. В режиме регенерации текстовой информации адресация ячеек памяти БЗУ осуществляется с помощью счетчика знакомест Счзни счетчика текстовых строк Счтс(см. рис. 2.6). Содержимое этих счетчиков изменяется синхронно с разверткой изображения.

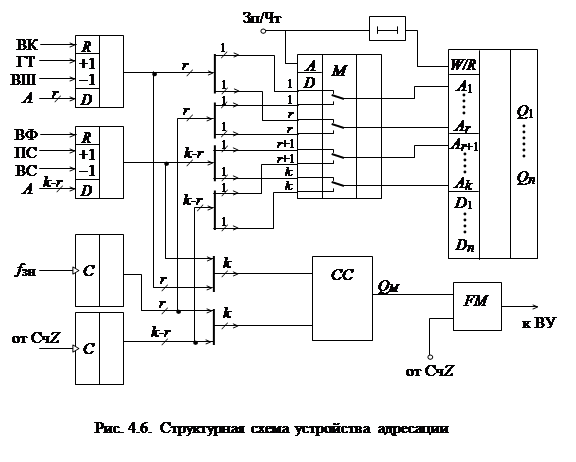

Запись информации в БЗУ в терминальных СОИ осуществляется от ЭВМ или с помощью устройства ручного ввода информации оператором. При вводе информации оператор должен видеть, в какую часть информационного поля она вводится. Для этой цели на экране формируется специальная метка, именуемая маркером (FM – узел формирования маркера). Маркер (см. рис. 4.6) может иметь конфигурацию прямоугольника, обрамляющего знакоместо, треугольника или полоски под знаком и т. д.

|

Адрес маркера задается счетчиком маркера СЧМ,состоящим из двух частей: счетчика знакомест СЧМзн,включающего в себя r младших разрядов адреса, и счетчика текстовых строк СЧМтс,включающего в себя (k-r)старших разрядов адреса. Счетчик маркера определяет его место на экране и статический адрес для ввода информации. Адрес в счетчик маркера вводится от источника информации с помощью соответствующих команд. Управляющие сигналы, формируемые под воздействием некоторых команд, показаны на рис. 4.6, где BK - возврат каретки (сбрасывается на ноль содержимое СЧМзни маркер переводится на первое место той же текстовой строки); ГТ- горизонтальная табуляция (содержимое СЧМзнувеличивается на единицу, в результате чего маркер сдвигается вправо на одно знакоместо); ВШ - возврат на шаг (содержимое СЧМзнуменьшается на единицу, в результате чего маркер сдвигается влево на одно знакоместо). Для записи произвольного адреса в счетчик маркера можно использовать входы D параллельного ввода информации в СЧМзни СчМтс.

В режиме записи подключение выходов счетчика маркера к адресным входам БЗУ осуществляется мультиплексором М. В режиме считывания (регенерации) мультиплексор подключает к адресным входам БЗУ выходы счетчика регенерации. Изменение режима ЗАПИСИ/ЧТЕНИЯ осуществляется по команде ЗП/ЧТ, воздействующей на мультиплексор, и через схему задержки на соответствующий вход БЗУ. Маркер формируется по сигналу Qм снимаемому с выхода компаратора кодов CC,сравнивающего коды адреса с выхода счетчика регенерации и с выхода счетчика маркера. Этим обеспечивается привязка маркера к адресуемому знакоместу на ИП. Сигнал Qм поступает на вход схемы формирования маркера FM.

Рассмотрим подробнее работу отдельных узлов устройства адресации.

Мультиплексор М - устройство, осуществляющее коммутацию цифровых сигналов с p информационных входов на один выход, т. е. коммутацию из p направлений в одно (из p в 1). Адрес коммутируемого направления задается кодовой комбинацией, подаваемой на адресные входы M. Таким образом, функция, реализуемая мультиплексором, может быть записана как

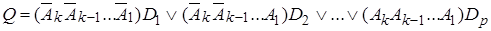

, (4.39)

, (4.39)

где (Ak, … A1)-сигналы на адресных входах; (Dp, … D1) -сигналы на информационных входах; Q -информационный выход М, k = [log2p] - число разрядов адресных входов M.

Логическое произведение адресных сигналов равно единице только для той входной переменной Di, индекс которой совпадает с требуемым адресом. Выражение (4.39) показывает, что мультиплексор может использоваться не только для коммутации сигналов, но и для реализации различных логических функций. Для этого переменные подаются на адресные входы, значение функции, соответствующее каждой комбинации переменных, задается на информационных входах, сама функция снимается с выхода М. Примером такого применения мультиплексора является схема формирователя напряжения развертки, рассмотренного выше в пункте 3.6.

При необходимости коммутации одновременно s групп цепей из p направлений в s направлений (s из р в 1) используется s мультиплексоров, коммутирующих р входов на один выход (из р в 1). В рассматриваемой схеме адресации (см. рис. 4.6) необходима коммутация k сигналов с двух направлений (р = 2) от счетчика регенерации и от счетчика маркера на k направлений (s = k),т. е, необходим мультиплексор с организацией k (из 2 в 1), где k - число адресных разрядов БЗУ. Для коммутации двух направлений число адресных входов мультиплексора kм = 1.

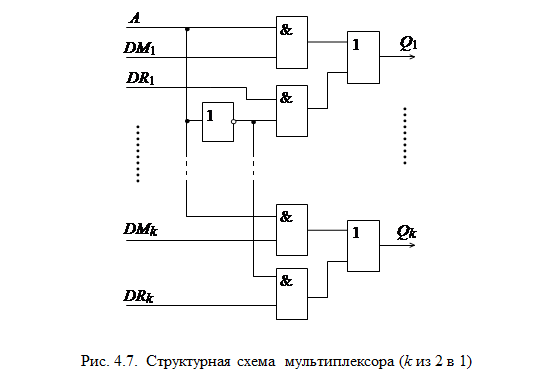

На рис. 4.6 показан электромеханический аналог такого мультиплексора. Схема реализует систему логических уравнений

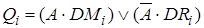

, 1≤ i≤ k,(4.40)

, 1≤ i≤ k,(4.40)

где Qi - сигнал на i-м информационном выходе М; А - сигнал на адресном входе М; DMi - сигнал с i-го разряда счетчика маркера; DRi - сигнал с i-го разряда счетчика регенерации; k - число адресных разрядов БЗУ.

На рис. 4.7 показана структурная схема мультиплексора, реализующая систему уравнений (4.40) с помощью логических комбинационных элементов. В качестве адресного сигнала в устройстве адресации используется сигнал управления режимом ЗАПИСЬ/ЧТЕНИЕ.

Мультиплексоры выпускаются в виде микросхем средней степени интеграции. Распространены ИМС мультиплексоров (4 из 2 в 1) К531КШ1, (2 из 4 в 1) К531КП2, К155КП2, К564КП1, (1 из 8 в 1) К531КП1, К155КП5, К564КП2, (1 из 16 в 1) К155КП1.

|

Возможно наращивание числа коммутируемых направлений за счет увеличения числа интегральных схем. Принцип наращивания числа направлений мультиплексора аналогичен принципу наращивания числа ячеек памяти ЗУ. Число интегральных схем мультиплексоров выбирают из условия m = [p/pм],где p - требуемое число коммутируемых направлений, pм - число направлений, коммутируемых микросхемой.

Адресные входы всех ИМС мультиплексоров объединяются и на них подаются младшие разряды адресации. Старшие разряды используются для выбора соответствующей интегральной схемы мультиплексора. Выходы ИМС мультиплексоров объединяются по правилам, рассмотренным выше для объединения выходов ЗУ.

Компараторы кодов CC служат для сравнения двух многоразрядных двоичных слов А и В. В общем случае компараторы кодов определяют следующие соотношения: A = B; A > B; A < B.

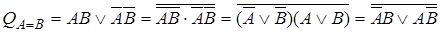

В устройстве адресации СОИ компаратор кодов формирует единичный сигнал при равенстве кодов с выхода счетчика регенерации и с выхода счетчика маркера (A = B). Для одноразрядных слов равенство кодов выполняется при А = 0, В = 0и при A = 1, В = 1. Следовательно, сигнал с выхода СС

. (4.41)

. (4.41)

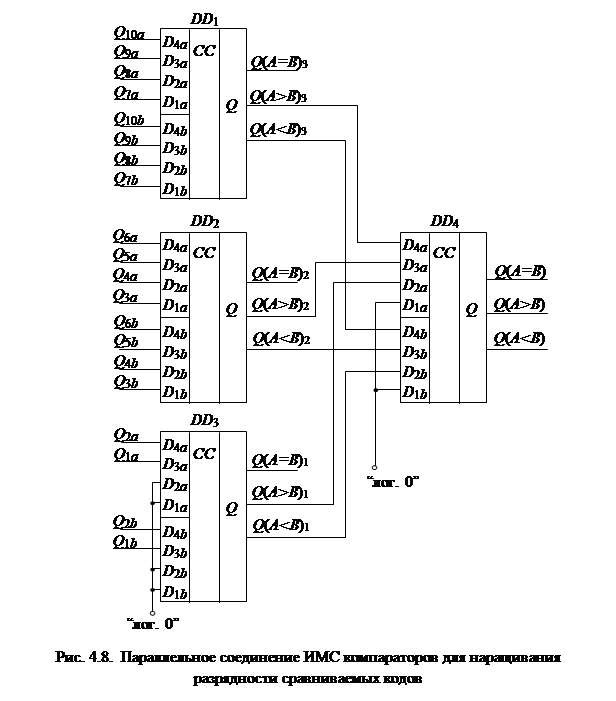

На рис. 4.8 показано параллельное соединение четырехразрядных ИМС для реализации десятиразрядного компаратора кодов.

|

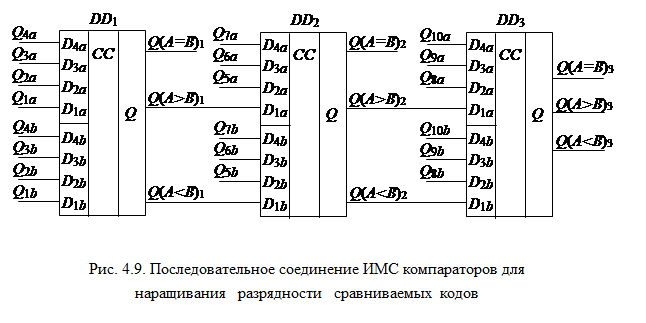

Некоторое сокращение числа ИМС в компараторе кодов при наращивании разрядности можно получить при последовательном соединении микросхем. Пример такой реализации десятиразрядного компаратора кодов показан на рис. 4.9.

|

В некоторых интегральных схемах компараторов кодов (например, в ИМС серий 531 и 564) имеются дополнительные выводы для последовательного наращивания разрядности сравниваемых кодов. Недостатком последовательного соединения ИМС компараторов является увеличение задержки срабатывания схемы.

Дата добавления: 2017-05-02; просмотров: 1541;