Микроархитектура процессоров 8086 и Pentium Pro

Структура Intel x86.

Первым представителем семейства Intel x86, или, согласно официальной классификации фирмы Intel (Integrated Electronics, США), семейства процессоров IA (Intel Architecture), является микропроцессор 8086, разработанный к 1978 году. Программы, написанные для него, выполняются на всех последующих процессорах семейства, включая все современные модели.

Микроархитектура процессоров 8086 и Pentium Pro

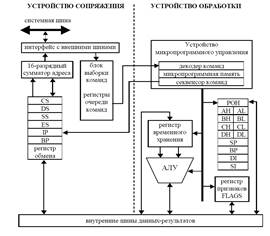

Микропроцессор 8086 ориентирован на выполнение команд параллельно с их выборкой и может быть условно разделен на две части, работающие асинхронно (см рис. ниже):

- устройство сопряжения с внешними шинами (УС);

- устройство обработки (УО).

Устройство сопряжения обеспечивает формирование 20-разрядного физического адреса памяти, выборку команд и операндов из памяти, организацию очередности команд и запоминание результатов выполнения команд в памяти. В состав УС входит шесть 8-разрядных регистров очереди команд, четыре 16-разрядных сегментных регистра, 16-разрядный регистр обмена и 16-разрядный сумматор адреса, интерфейс с внешними шинами. Регистры очереди команд организованы по принципу FIFO - «первым пришел - первым вышел». УС готово выполнить цикл выборки 16-разрядного слова из памяти всякий раз, когда в очереди освобождаются, по меньшей мере, два байта, а УО извлекает из очереди команды по мере их выполнения. При выполнении команд передачи управления, например условных и безусловных переходов, очередь очищается УС и начинает заполняться заново.

Рисунок 1.Микроархитектура процессора Intel 8086.

Устройство обработки предназначено для выполнения операций по обработке данных и состоит из устройства микропрограммного управления (УМУ), 16-разрядного АЛУ, восьми 16-разрядных регистров общего назначения и регистра признаков. Команды из очереди, сформированной УС, поступают в УМУ, где декодируются и выполняются в 16-разрядном АЛУ согласно процедурам, записанным в памяти микропрограмм. Последовательное выполнение команд обеспечивается секвенсором команд, часть которого (регистр счетчика команд IP) изображена в составе УС, т.к. именно УС записывает в IP смещение следующей команды, т.е. положение новой команды относительно начала сегмента команд. УО обменивается данными с УС через внутреннюю 16-разрядную шину и регистр обмена.

Для сравнения приводится (рис. 2) микроархитектура процессоров 39 шестого поколения Pentium Pro. Как видно, архитектура со времени 8086 претерпела не только количественные (разрядность внутренних и внешних шин данных, регистров), но и существенные качественные изменения. Pentium Pro имеет суперскалярную архитектуру, т.е. может одновременно вы-полнять несколько команд за один такт. Эту возможность обеспечивают несколько АЛУ - два блока целочисленной арифметики и два блока с плавающей точкой. Другая важная особенность – т.н. динамическое исполнение – команды разбиваются на простейшие операции, порядок независимого исполнения которых определяется блоком «завершения и удаления микрокоманд» с буферами переупорядочивания и пулом микрокоманд (рис. 2.).

Рисунок 2. Микроархитектура процессора Pentium Pro.

На рис. 3 представлены обозначения микропроцессоров для принципиальных электрических схем, на которых видны внешние шины и сигналы 16-разрядного 8086 и 32-разрядного 80486.

Рисунок 3. Обозначения микропроцессоров для принципиальных электрических схем.

Регистры.

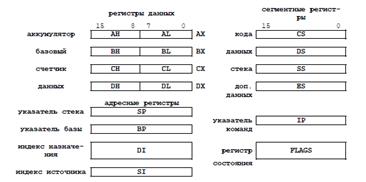

Микропроцессор 8086 имеет 12 программно-доступных шестнадцатиразрядных регистров, регистр счетчика команд IP (Instruction Pointer) и регистр флагов (или регистр состояния процессора) FLAGS.

Среди программно-доступных регистров выделяют следующие группы (см. рис. 4):

- Регистры данных: AX – аккумулятор (Accumulator); BX - базовый регистр (Base); CX - регистр счетчика (Counter); DX - регистр данных (Data).

- Регистры-указатели (индексные регистры): SI - индекс источника (Source Index); DI - индекс приемника (Destination Index); BP - указатель базы (Base Pointer); SP - указатель стека (Stack Pointer).

- Сегментные регистры: SS - сегмент стека (Stack Segment); DS - сегмент данных (Data Segment); ES - дополнительный сегмент (Extended data Segment); CS – сегмент кода (Code Segment).

16-битные регистры AX, BX, CX, DX состоят из двух 8-битных половин, к которым можно независимо обращаться по именам AH, BH, CH, DH - старшие байты и AL, BL, CL, DL - младшие байты.

Рисунок 4. Регистры процессора 8086.

Биты (или флаги) регистра признаков FLAGS разделяются на условные, отражающие результат предыдущей операции ALU, и управляющие, от которых зависит выполнение специальных функций.

Рисунок 5. Флаги процессора Intel 8086.

Флаги TF, IF, DF относятся к управляющим флагам, остальные - к условным (флагам состояния). Флаги отражают следующие условия:

- флаг переноса CF устанавливается в 1 при переносе/заеме, возникающем при сложении/вычитании байтов или слов, а также принимает значение выдвигаемого бита при сдвигах операнда;

- флаг четности PF устанавливается в 1, если младшие 8 бит результата имеют четное число единиц;

- флаг вспомогательного переноса AF устанавливается в 1, если есть перенос/заем из младшей тетрады в старшую 8- или 16-битного результата в операциях десятичного сложения/вычитания;

- флаг нуля ZF устанавливается в 1 при нулевом результате операции;

- флаг знака SF устанавливается в 1 при отрицательном результате операции при использовании дополнительного кода;

- флаг переполнения OF устанавливается в 1 при потере старшего бита результата сложения или вычитания;

- если флаг направления DF установлен в 1, то используется автодекрементная адресация при выполнении операции обработки строк, если DF установлен в 0, то используется автоинкрементная адресация;

- если флаг прерывания IF установлен в 1, то внешние маскируемые прерывания разрешены, иначе запрещены;

- если флаг трассировки TF установлен в 1, то процессор переходит в состояние прерывания после выполнения каждой операции, что позволяет проводить пошаговую отладку программ.

Дата добавления: 2021-06-28; просмотров: 529;