Параллельное разветвление

Параллельное разветвление отвечает обработке ветвей по логике И. Параллельное разветвление начинается общим переходом, который активирует первый шаг во всех параллельных ветвях.

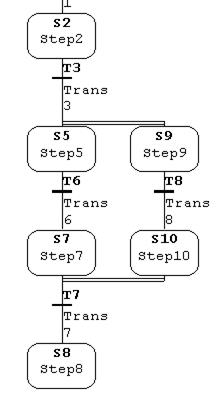

На рисунке 4.4 общими переходами являются переходы Т3 и Т7.

Параллельное разветвление заканчивается шагом, подключенным к общему финальному переходу. Финальный переход позволяет следующий шаг только тогда, когда выполнены все параллельные ветви.

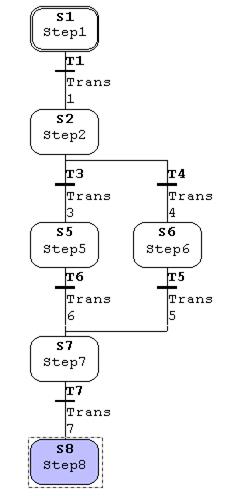

Рисунок 4.3 - Секвенсор с альтернативными ветвями

Рисунок 4.4 – Секвенсор с параллельными ветвями

Постоянные условия

Условия, которые нужно выполнять в более чем одной точке секвенсора, могут быть запрограммированы как постоянные условия.

Для программирования условий можно использовать элементы контактной схемы – нормально разомкнутые или нормально замкнутые контакты, компараторы или элементы FBD. В постоянном условии можно использовать до 32 элементов.

Результат вычисления условий хранится элементом «катушка» в LAD или блоком памяти в FBD.

Вызовы блока

Блоки, созданные на других языках программирования, могут быть вызванны с использованием постоянных инструкций или действий в FB S7-GRAPH. После того, как вызванный блок будет выполнен, выполнение FB S7-GRAPH будет продлено.

В S7-GRAPH можно вызвать функции (FC) и функциональные блоки (FB), запрограммированные на LAD, FBD, STL или SCL, а также системные функции (SFC) и системные функциональные блоки (SFB). Функциональным блокам и системным функциональным блокам должны быть назначены экземплярные блоки данных DB. Имена блоков можно использовать в абсолютном виде, например, FC1 или символьно, например, Motor1. При вызове блоков нужно обеспечить формальные параметры вызываемого блока действительными значениями.

Дата добавления: 2016-12-09; просмотров: 2736;