Рассмотрим различные ситуации при вычитании.

1) Вычислим в двоичных кодах результат операции 7-5 = 7+(-5).

Определим дополнительный код –5 = -00000101пр = 11111011доп.

Тогда 710-510 = 00000111доп+11111011доп = 1.00000010доп = 00000010пр = 210

Возникший перенос 1 в разряд D8 отбрасывается. Знаковый разряд D7 = 0, поэтому результат – положительное число 2, у которого прямой код такой же, как и дополнительный.

2) Определим результат операции 510-710 = 00000101пр-00000111пр = 00000101доп+11111001доп = 11111110доп = -00000010пр=-210

Здесь D7 = 1, результат отрицательный, поэтому дополнительный код переводится в прямой. Это выполняется по тому же правилу, что и перевод прямого кода в дополнительный.

3) Найдём –510-710 = 11111011доп+11111001доп=1.11110100доп = -00001100пр = -1210.

Умножение

Операция выполняется также как и для десятичных кодов: множимое умножается на каждый разряд множителя и результаты складываются со сдвигом. Можно умножать, начиная с младших разрядов со сдвигом влево, или со старших со сдвигом вправо.

610* 710 111 111

*110 *110

000 111

111 111

*111 * 000

1010102 = 4210 101010

Числа со знаком умножаются в прямом коде, а знак определяется как сумма по модулю 2 знаковых разрядов.

Деление

Выполняется как вычитание со сдвигом. Например:

18:6 = 3 22:4 = 5,5

10010 : 110 10110 : 100

- 110 11 - 100 101,1

110 110

- 110 - 100

000 10,0

- 100

000

Здесь дробная часть представляет отрицательные степени числа 2.

Например: степени 2 2 1 0 -1 -2

Код 110,11 = 4+2+0,5+0,25 = 6,75.

Типовые комбинационные микросхемы

Дешифраторы

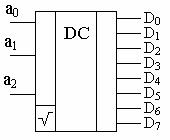

Дешифратор – логический узел, осуществляющий коммутацию одного из N выходов по заданным n адресным входам. На рис 5-1 показан дешифратор 3х8 (3 адресных входа, 8 выходов). При подаче на входы а0а1а2 какого-либо кода на выходе с номером определенным адресным кодом появляется 1, а на остальных выходах - 0. Дешифратор используется для выбора (коммутации) одного из блоков цифрового устройства.

Рис 5-1 Дешифратор

Если число выходов N < 2n, то дешифратор называется неполным.

При стробсигнале √ = 0 все выходы обнулены.

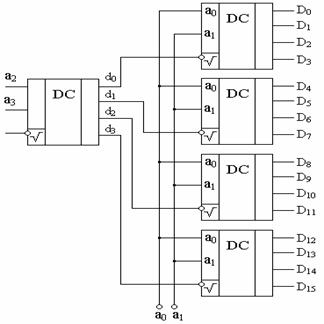

Двухъярусная схема

При большом числе выходов применяются двухъярусные схемы с использованием стробирующих входов. Если имеется k – разрядный дешифратор, то для n > k потребуется 2n-k+1 дешифраторов.

Например, требуется построить дешифратор 4х16 используя дешифраторы 2х4. В этом случае n = 4, а k = 2, и потребуется 24-2+1 = 5 дешифраторов.

Рис.5-2 Двухярусный дешифратор

Дата добавления: 2016-11-29; просмотров: 1425;