ТАЙМЕР НА ИНТЕГРАЛЬНЫХ МИКРОСХЕМАХ СЕРИИ К155

Таймер имеет следующие параметры: максимальная выдержка 9999 с (дискрет 1 с) и 999,9 с (дискрет 0,1 с), точность выдержки определяется точностью частоты сети, набор времени — кнопочный, аналогично набору чисел в микрокалькуляторах, возможно многократное повторение один раз набранной выдержки, на табло индицируется оставшееся до окончания выдержки время.

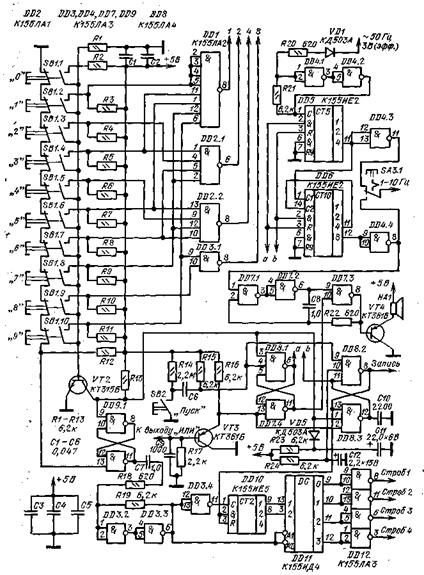

Блок управления (рис. 61) содержит шифратор (многокнопочный переключатель SB1, микросхемы DDlt DD2, DD3.1) распределитель строб-импульсов (DD9, DD3.2, DD3.3, DD3.4, DD10, DD11, DD12), формирователь счетных импульсов (DD4, DD5, DD6), генератор звукового сигнала (DD7.1, DD7.2, DD7.3), триггеры управления (DD9.1 и DD9.2, DD8.1 и DD7.4, DD8.2 и DD8.3).

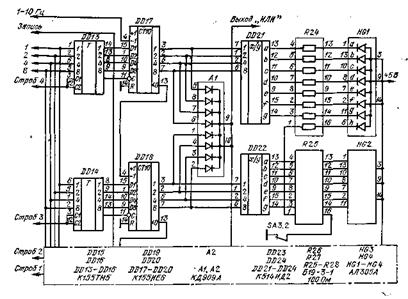

Счетная часть (рис. 62) содержит регистр памяти (DD13 — DD16), счетчик (DD17 — DD20), диодный элемент ИЛИ (матрицы А1 и А2), преобразователи кода 1 — 2 — 4 — 8 в коды семисегментного индикатора (DD21 — DD24), резистор-ные блоки (R24 — R27), семисегментные полупроводниковые индикаторы АЛ305А (HG1 — HG4). На рис. 62 развернута половина схемы. Нижняя часть схемы отличается от верхней отсутствием цепи зажигания десятичной точки (SA3.2, нижние резисторы резисторных блоков R24 и R25, сегмент h — точка HQ1).

При нажатии на одну из кнопок переключателя SB1 (см. рис. 61) на выходах 1 — 2 — 4 — 8 шифратора появляется код, соответствующий нажатой кноп-ке. Одновременно входной ток ИС шифратора вместе с током одного из резисторов R2 — R11 включает транзистор VT2, который, в свою очередь, устанавливает все триггеры в необходимые состояния. Спад положительного импульса с выхода 11 DD9.2 дифференцируется цепочкой C7R18 и формируется в прямоугольный импульс отрицательной полярности триггером Шмитта DD3.2, DD3.3. Этот импульс обеспечивает выдачу импульса отрицательной полярности с выхода 0 стробируемого по входам А1 и А2 дешифратора DD11. После инвертирования элементом DD12 с выхода 8 этот импульс в положительной полярности поступает на вход стробирования ИС регистра памяти DD16 (см. рис. 62), на информационные входы которой поступает код с выходов шифратора! Происходит запись кода в триггеры этой микросхемы. Уровень логического О о выхода DD8.2 поступает на входы записи ИС DD17 — DD20 и разрешает перепись кода из регистра памяти в счетчик. Состояние DD20 преобразуется в код семисегментного индикатора, который поступает на индикатор HG4.

Рис. 61. Схема блока управления таймера

Емкость конденсатора С7 (см. рис. 61) подобрана такой, что импульс, формируемый на выходе DD3.3, заканчивается после окончания дребезга контактов нажимаемой кнопки, что обеспечивает правильность записываемого в регистр памяти кода.

Спадом импульса положительной полярности с выхода DD3.4 счетчик DD10 переключается в состояние 1. В момент отпускания нажатой кнопки переключателя SB1 триггер DD9.1, DD9.2 переключается в исходное состояние.

Следующее нажатие любой кнопки переключателя SB1 приводит к формированию импульса на очередном выходе DD12 и записи кода нажатой кнопки в очередную ИС регистра памяти DD15, DD14, DD13 и счетчика DD19, DD18, DD17 (см. рис. 62). Процесс записи контролируется по индика-торам HG1 — HG4. После четырех нажатий на кнопки SB1 информация в регистре и счетчике полностью обновляется. Если в процессе набора выдержки допущена ошибка, набор можно повторить.

Импульсы счета времени формируются из частоты сети 50 Гц. Напряжение 3 В с обмотки трансформатора триггером Шмитта DD4.1, DD4.2 (см, рис. 61) преобразуется в импульсы и делится до частоты 10 Гц микросхемой DD5 и до 1 Гц микросхемой DD6. Выбор необходимой частоты осуществляется переключателем SA3.1. При частоте 10 Гц на индикаторе HG1 переключателем SA3.2 зажигается десятичная точка. Во время набора времени деление частоты сети блокировано сигналами с уровнем логической 1, поступающей с выходов DD8.3 и DD8.1.

Рис. 62. Схема счетной части таймера. (Вход Запись подключен ко входам DD17 — DD20.)

При нажатии на кнопку SB2 (Пуск) триггер DD8.2, DD8.4 переключается в противоположное состояние. Уровень логической 1 с выхода DD8.2 устанавливает в состояние 0 счетчик D10 и, поступая на входы ИС счетчика

DD17, DD20 (см. рис. 62), блокирует перепись информации из регистра памяти в счетчик. Уровень логического 0 с выхода DD8.3 (см. рис. 61) поступает на входы R DD5 и DD6 и разрешает деление частоты сети.

Импульсы с выходов DD5 и DD6 через инверторы DD4.3 и DD4.4 через переключатель SA3.1 поступают на вход вычитания микросхемы DD17 (см. рис. 62). Инверторы обеспечивают необходимую полярность импульсов счета.

Содержимое счетчика начинает уменьшаться. Процесс счета контролируется на индикаторах HG1 — HG4. В момент времени, когда счетчик досчитает до 0, уровень логического 0 с выхода элемента ИЛИ, собранного на двух диодных матрицах А1 и А2 и резисторе R17, через согласующий эмиттер-ный повторитель VT3 поступает на входы элементов DD7.4 и DD8.3 и устанавливает триггеры в противоположные состояния. Сигнал логического 0 с выхода DD8.2 (см. рис. 61) производит перепись информации из регистра памяти DD13 — DD16 в счетчик, благодаря чему процесс счета блокируется.

Сигнал логической 1 с выхода DD7.4 поступает на вход 10 DD7.3 и разрешает генерацию звукового сигнала в генераторе DD7.1, DD7.2, DD7.3. Поскольку деление частоты сети разрешено сигналом логического 0, поступающим на входы R DD5 и DD6, с выхода DD8.1 на вход 1 DD7.1 поступает меандр с частотой 1 Гц и звуковой сигнал прерывается с такой же частотой. Сигнал будет звучать до тех пор, пока не будет нажата одна из кнопок переключателя SB1 или кнопка Пуск. В первом случае переключится только триггер DD8.1, DD7.4, прекратится звучание сигнала и блокируется деление частоты. При последующем нажатии кнопки Пуск будет обеспечена необходимая фаза счетных импульсов.

Если же кнопка Пуск будет нажата при звучащем сигнале, фаза импульсов счета будет случайной и пуск возможен с ошибкой в сторону уменьшения выдержки, не превышающей величины дискрета (0,1 с или 1 с).

Цепь R14C6 исключает ложный пуск таймера в момент отпускания SB2 из-за дребезга контактов. Элементы R23, R24, СИ, С12, VD5 обеспечивают исходное состояние триггеров и счетчика DD10 при включении таймера в сеть.

Электромагнитное исполнительное реле может быть подключено между выходом DD8.1 и цепью +5 В, если его рабочий ток не превышает 20 мА при напряжении +5 В (герконовое реле РЭС-55), или через эмиттерный повторитель на транзисторе КТ361 с любым индексом (РЭС-LO или РЭС-15 на рабочее напряжение 5 В).

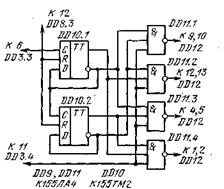

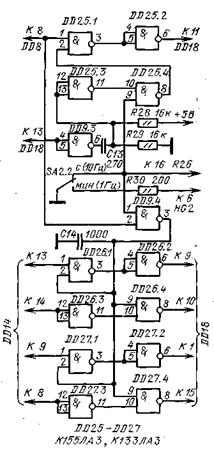

Интегральные микросхемы К155ИЕ5 и К155ИД4 можно заменить менее дефицитными К.155ТМ2 и КД55ЛА4 (рис. 63), одновременно необходимо в качестве DD9 также установить К.155ЛА4. В связи с тем что полярность входных импульсов для К155ТМ2 другая, чем у КЛ55ИЕ5, подключение входа с DD10.1 и входов стробирования изменено, сигнал установки 0 снимается с другого плеча триггера (DD8.3 на рис. 61).

Если многократное повторение выдержки не требуется, из схемы таймера можно исключить регистр памяти DD13 — DD16 (см. рис. 62), а также микросхему DD12 (см. рис. 61). В этом случае выходы 1, 2, 4, 8 шифратора подключают к соответствующим входам DD17 — DD20, а выходы дешифратора — непосредственно ко входам DD17 — DD20. Инверторы DD12 не требуются, так как полярность импульсов записи DD17 — DD20 отрицательная и совпадает с полярностью выходных импульсов дешифратора DD11. В этом случае необходимо также между эмиттером VT3 и входами DD7.4 и DD8.3 включить дифференцирующую цепочку, аналогичную C1R4R5 на рис. 60. Емкость конденсатора этой цепочки следует увеличить до 0,047 мкФ.

В таймере использованы резисторы МЛТ-0,125 и МЛТ-0,25, конденсаторы КМ-5а (С1 — С6) и КМ-6 (С7 — С8), переключатели П2К (два пятикнопоч-ных без фиксации — SB1, однокнопочные без фиксации — SB2 и с фиксацией — SB3 и не показанный на схеме выключатель сети SA4). Головка НА1 — любая электромагнитная с сопротивлением 30 — 100 Ом или динамическая 4 — 8 Ом, включенная через выходной трансформатор от любого транзисторного приемника.

Рис. 63. Схема замены интегральных микросхем К155ИЕ5 и К155ИД4 на К155ТМ2 и К155ЛА4. (В качестве DD11.4 должен быть установлен DD9.3.)

Семисегментные индикаторы АЛ305А, можно заменить любыми другими с общим анодом, например АЛ304Г, АЛС324Б, или при замене микросхем К514ИД2 на К514ИД1 — индикаторами с общим катодом (АЛ304А, АЛ304Б, АЛС314А), одновременно исключив ре-зисторные блоки. Диодные матрицы КД909 можно заменить на КД903, КД908, КДС627.

При отсутствии переключателей П2К в качестве SB1 можно применить любые другие кнопки, однако их конструкция должна быть такой, чтобы при нажатии вначале размыкались нормально замкнутые, затем замыкались нормально разомкнутые контакты. Кнопки КМ-2 требуют специальной регулировки подгибанием пружины.

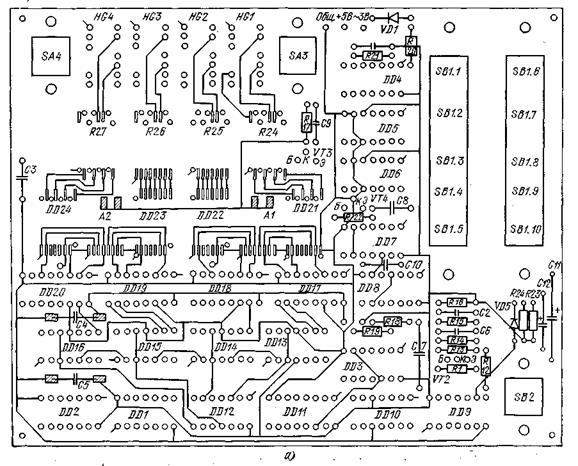

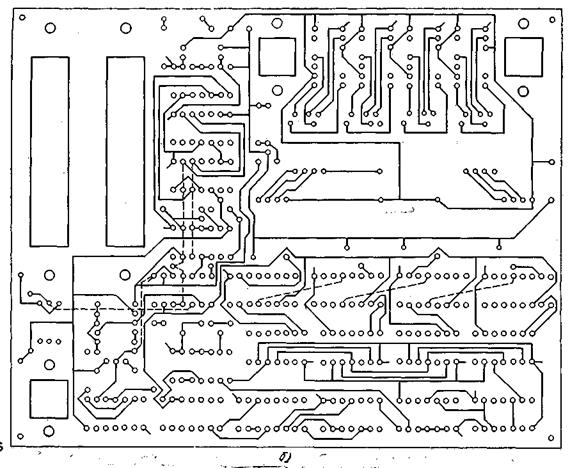

Все элементы таймера, в том числе и переключатели, установлены на двусторонней печатной плате, чертеж которой приведен на рис. 64. Настройки таймер не требует. При желании можно подобрать емкость конденсатора С8 для получения необходимой высоты тона сигнала. При применении в качестве SB1 кнопок другого типа может потребоваться подбор емкости С7. Блок питания таймера должен обеспечивать напряжение 5 В при токе до 0,8 А.

Если необходимо, таймер можно доработать так, чтобы набор времени осуществлялся в минутах и секундах. Схема такой доработки приведена на рис. 65. В положении SA2, указанном на рис. 65, таймер работает, как описано выше, — частота импульсов заполнения счетчика 10 Гц, цена младшего разряда 0,1 с, зажжена запятая перед индикатором HG1.

При переводе переключателя SA2 на рис. 65 в нижнее по схеме положение зажигается запятая перед индикатором HG2 (см. рис. 61), разделяющая минуты (индикаторы HG3 и HG4) и секунды (HG1, HG2). Элемент DD25.4 разрешает прохождение инвертированных элементов DD9.3 и продифференцированных цепочкой C13R28R29 импульсов с выхода 13 DD18 на вход 11 той же ИС. В результате каждый раз в момент спада отрицательного импульса на выходе 13 DD18 на вход И DD18 поступает короткий отрицательный импульс, производящий запись кода, поступающего на входы 9, 10, 1, 15 DD18 с выходов элементов DD26.2, DD26.4, DD27.2, DD27.4. В нижнем по схеме положении переключателя SA2.2 и уровне логической 1, поступающем с выхода 5 DD8, на выходах указанных элементов код цифры 5, в результате чего DD18 переходит в состояние 5 и коэффициент ее пересчета равен шести. При записи исходного состояния импульс отрицательной полярности с выхода 8 DD8 подключает ко входам DD18 сигналы с выхода DD14 независимо от положения переключателя SA2.2.

Максимальная выдержка времени в доработанном таким образом таймере составляет 99 мин 99 с, т. е. несколько более 100 мин.

Интегральные микросхемы DD25 — DD27 можно разместить на небольшой печатной плате, размещенной над свободным от элементов месте основной платы. Для уменьшения размеров дополнительной платы целесообразно при доработке использовать ИС серий К.133 или К.136.

Рис. 64. Печатная плата таймера со стороны установки микросхем (а) и с противоположной стороны (б)

Рис. 65. Схема доработки таймера

Дата добавления: 2016-06-18; просмотров: 4273;