Микропроцессорный комплект серии К580

В МПК серии К580 процессор вместе с устройством управления реализован в виде отдельной БИС и имеет фиксированные разрядность и систему команд, «зашитую» в БИС МП. Микро-ЭВМ, построенная на МПК с фиксированной разрядностью и ограниченным количеством магистралей, имеет типичную для данного типа МПК структуру. Изучение особенностей построения микро-ЭВМ на МПК серии К580 позволит легко освоиться с работой других аналогичных МПК.

Микропроцессорный комплект серии К580 включает в себя микросхемы: 1. Микропроцессорная БИС. 2. Программируемое устройство ввода — вывода параллельной информации различного формата КР580ВВ55. 3. Программируемый блок приоритетного прерывания КР580ВН59. 4. Программируемое устройство прямого доступа к памяти КР580ВТ57. 5. Интегральный таймер КР580ВИ53. 6. Универсальный синхронно-асинхронный программируемый приемопередатчик КР580ВВ51. 7. Программируемый контроллер электроннолучевой трубки КР580ВГ75. 8. Программируемый контроллер клавиатуры КР580ВВ79. 9. Системный контроллер КР580ВН28.

Схемы выполнены по п-МОП-технологии, входные и выходные сигналы соответствуют уровням работы ТТЛ-схем. Микро-ЭВМ, построенная на базе комплекта, работает с тактовой частотой до 2 МГц. Схемы программируются с помощью фиксированного набора команд МП БИС КР580ВМ80.

Ограничения по количеству магистралей в МПК такого типа приводят к необходимости организации последовательной обработки информации, что обусловливает относительно медленное выполнение команд. При тактовой частоте генератора 2 МГц время выполнения команд колеблется от 2 до 8 мкс.

Микропроцессорная БИС КР580ВМ80. Микропроцессорная БИС КР580ВМ80 представляет собой однокристальный 8-разрядный МП с двумя магистралями: однонаправленной 16-разрядной адресной магистралью (МА), двунаправленной 8-разрядной магистралью данных (МД), и 12 сигналами управления (шесть входных и шесть выходных) (рис. 7.1).

Микропроцессорная БИС рассчитана на выполнение логических и арифметических операций с 8-разрядными числами в двоичной и десятичной системах счисления, а также операций с двойной разрядностью (с 16-разрядными числами).

Функциональное назначение внешних выводов МП БИС КР580ВМ80:

—адресная магистраль (выходы с тремя состояниями), обеспечивающая адресацию к любой из

—адресная магистраль (выходы с тремя состояниями), обеспечивающая адресацию к любой из  8-разрядной ячейки памяти или внешнего устройства (ВУ);

8-разрядной ячейки памяти или внешнего устройства (ВУ);

— двунаправленная магистраль данных, используемая для обмена информации с памятью или ВУ;

— двунаправленная магистраль данных, используемая для обмена информации с памятью или ВУ;

СИНХР (синхронизация) — на этом выходе МП БИС формируется сигнал СИНХР в начале каждого машинного цикла;

П (прием) — сигнал ПРИЕМ на этом выходе указывает на готовность МП БИС к приему данных;

ОЖД (ожидание) — сигнал ОЖД на этом выходе указывает, что МП находится в состоянии ожидания;

— на этом выходе МП-БИС сигнал

— на этом выходе МП-БИС сигнал  указывает, что данные выданы МП БИС и установлены на МД и могут быть записаны в ВУ;

указывает, что данные выданы МП БИС и установлены на МД и могут быть записаны в ВУ;

а)

Рис. 7.1. Схема МП БИС КР580ВМ80 (а) и ее условное обозначение (б)

б)

Рис. 7.1. (б) условное обозначение.

П.ЗХ (подтверждение захвата) — на этом выходе МП БИС сигнал П.ЗХ появляется в ответ на сигнал З.ЗХ (запрос захвата) и указывает, что МД и МА находятся в состоянии высокого сопротивления;

Р.Пр (разрешение прерывания) — на этом выходе сигнал Р.Пр указывает на состояние внутреннего триггера разрешения прерывания МП БИС. Состояние триггера может быть установлено программно с помощью команд EI, DI. При уровне «0» на выходе Р.Пр прием запросов прерывания МП БИС невозможен;

Г (готов) — сигнал ГОТОВ на этом входе информирует о готовности ВУ к обмену информацией с МП БИС. При уровне «0» МП БИС будет находиться в состоянии ОЖИДАНИЕ.

З.ЗХ (запрос захвата) — вход, используемый для подачи сигнала З.ЗХ на переход МП БИС в состояние ЗАХВАТ, в котором МА и МД переходят в третье состояние (высокое сопротивление). Обычно состояние используется для организации обмена информацией по каналу прямого доступа к памяти;

З.Пр (запрос прерывания) — вход, используемый для подачи сигнала ЗПР. Сигнал поступает от внешнего устройства на прерывание выполнения основной программы и переход на выполнение подпрограмм обслуживания прерывания. Сигнал запроса прерывания не воспринимается МП БИС при работе его в режимах ЗАХВАТ, ОЖИДАНИЕ или нулевом состоянии внутреннего триггера разрешения прерывания;

R — вход, по которому поступает сигнал на начальную установку МП БИС, при этом обнуляются его программный счетчик, внутренние триггеры, формирующие сигналы Р.Пр и П.ЗХ;

— входы для подачи тактовых сигналов

— входы для подачи тактовых сигналов  . Последние являются не пересекающимися во времени сигналами, определяющими тактовую частоту работы МП БИС.

. Последние являются не пересекающимися во времени сигналами, определяющими тактовую частоту работы МП БИС.

Входы источников питания МП БИС: нулевой потенциал (земля) +5В, —5В, +12В. Условное обозначение схемы МП БИС КР580ВМ80 приведено на рис. 7.1,б.

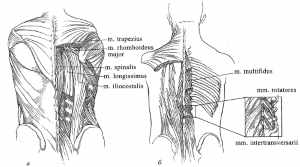

Структура МП БИС КР580ВМ80 приведена на рис. 7.1. Микропроцессорная БИС состоит из следующих функциональных блоков (рис. 7.1) [15] : 1) регистров и логических целей их выбора; 2) арифметическо-логического блока; 3) регистра команд и устройства управления (УУ); 4) буферов МД (БФД) и МА (БФА).

Секция регистров включает в себя шесть 16-разрядных регистров: W, Z; В, С; D, E; H, L; PC (программный счетчик) и SP (указатель стека). Шесть 8-разрядных регистров общего назначения составлены в пары регистров: B, С; D, E; H, L. Они могут быть использованы в программах как отдельные 8-разрядные регистры, а также как три 16-разрядных регистра (B; D; Н).

Программный счетчик РС содержит текущий адрес памяти, к которому обращается программа. Содержание РС автоматически изменяется в течение каждого цикла команды. Указатель стека SR содержит адрес памяти, начиная с которого ее можно применять для хранения и восстановления содержания программно-доступных регистров МП БИС.

Буферные регистры W, Z не являются программно-доступными регистрами и используются для выполнения команд внутри МП БИС.

Арифметическо-логический блок (АЛБ) выполняет арифметические и логические операции под воздействием устройства управления МП БИС. Он включает в себя 8-разрядное АЛУ, схему десятичной коррекции ДК, построенной на базе ПЗУ, 5-разрядный регистр признаков, аккумулятор А, буфер аккумулятора БФА и буферный регистр БФРг. Арифметическо-логический блок позволяет осуществить арифметические операции сложения, вычитания, а также основные логические операции (И, ИЛИ, исключающее ИЛИ) и сдвиг. При проведении операций одно число всегда берется из буфера аккумулятора, а другое — из буферного регистра. По результату выполнения арифметическо-логических операций АЛБ устанавливает в регистре признаков пять разрядов.

Признак переноса (Саггу — С) устанавливается в единицу, если при выполнении команд появляется единица переноса из старшего разряда.

Дополнительный признак переноса (Auxiliary сагrу— АС) устанавливается в единицу, если при выполнении команд возникает единица переноса из третьего разряда числа. Состояние разряда может быть проанализировано лишь командой десятичной коррекции числа,

Признак знака (Sign—S) в машинном слове можно представить числом от —128 до +127. В этом случае седьмой (старший) разряд числа—его знак. Единица в седьмом разряде при такой записи будет указывать на отрицательное число, а ноль — на положительное.

В разряд нулевого признака (Zего — Z) записывается единица, если при выполнении команды результат равен нулю.

В разряд признака четности (Раritу — Р) записывается единица, если при выполнении команды количество единиц в разрядах результата будет четным.

Регистр команд РгК и дешифратор команды ДШК используются в МП БИС для получения и дешифрации кода команды. При извлечении команды первый байт, содержащий ее код, помещается в регистр команды и поступает на дешифратор команд. Дешифратор совместно с устройством управления и синхросигналами  формирует управляющие сигналы для всех внутренних блоков МП БИС, а также его выходные сигналы управления и состояния.

формирует управляющие сигналы для всех внутренних блоков МП БИС, а также его выходные сигналы управления и состояния.

Выполнение каждой команды производится МП БИС в строго определенной последовательности, определяемой кодом команды, и синхронизируется во времени сигналами  тактового генератора.

тактового генератора.

Период синхросигналов  называется машинным тактом (Т). Длительность машинного такта Т может быть установлена произвольно в диапазоне от 0,5 до 2 мкс.

называется машинным тактом (Т). Длительность машинного такта Т может быть установлена произвольно в диапазоне от 0,5 до 2 мкс.

При использовании МП БИС необходимо ясно представлять динамику его работы, т. е. на каких магистралях, в зависимости от каких управляющих сигналов и когда МП БИС будет выдавать ту или иную информацию. Это в дальнейшем поможет понимать работу схем, позволяющих согласовывать ее с различными периферийными устройствами микро-ЭВМ.

При анализе процессов будем использовать следующие понятия: машинный цикл (М) — время, требуемое для извлечения 1 байт информации из памяти или выполнения команды, определяемой одним машинным словом. Машинный цикл может состоять из 3—5 машинных тактов. Время выполнения команды — время получения, декодирования и выполнения команды.

В зависимости от вида команды это время может состоять из 1—5 машинных циклов. Для МП БИС КР580ВМ80 существует десять различных типов машинных циклов: 1. Извлечение кода команды (  ). 2. Чтение данных из памяти. 3. Запись данных в память. 4. Извлечение из стека. 5. Запись данных в стек. 6. Ввод данных из внешнего устройства. 7. Запись данных во внешнее устройство. 8. Цикл обслуживания прерывания. 9. Останов. 10. Обслуживание прерывания при работе МП БИС в режиме останова.

). 2. Чтение данных из памяти. 3. Запись данных в память. 4. Извлечение из стека. 5. Запись данных в стек. 6. Ввод данных из внешнего устройства. 7. Запись данных во внешнее устройство. 8. Цикл обслуживания прерывания. 9. Останов. 10. Обслуживание прерывания при работе МП БИС в режиме останова.

Первым машинным циклом при выполнении любой команды всегда является цикл  извлечения кода команды. На первом такте каждого машинного цикла МП БИС указывает тип выполняемого цикла с помощью 8- разрядного слова состоянии, выдаваемого на МД.

извлечения кода команды. На первом такте каждого машинного цикла МП БИС указывает тип выполняемого цикла с помощью 8- разрядного слова состоянии, выдаваемого на МД.

а)

а)

орг

Рис. 7.2.Схема записи слова состояния МП БИС (а).

б)

б)

Рис. 7.2. (б) Временная диаграмма записи

Отдельные разряды слова состояния задействуются в микро-ЭВМ для формирования магистрали управления. Слово состояния выдается на МД лишь на интервале синхросигналов С (такты  и

и  ), а используется на протяжении всего машинного цикла, поэтому необходимо записать его в специальный регистр слова состояния РгСС. На рис. 7.2, а приведена схема записи слова состояния. Запись осуществляется с использованием сигнала С синхросигнала

), а используется на протяжении всего машинного цикла, поэтому необходимо записать его в специальный регистр слова состояния РгСС. На рис. 7.2, а приведена схема записи слова состояния. Запись осуществляется с использованием сигнала С синхросигнала  . Сигнал С появляется в начале каждого цикла и занимает промежуток времени между положительными фронтами синхросигнала

. Сигнал С появляется в начале каждого цикла и занимает промежуток времени между положительными фронтами синхросигнала  на тактах

на тактах  и

и  (рис. 7.2, б). Таким образом, запись слова состояния осуществляется сигналом

(рис. 7.2, б). Таким образом, запись слова состояния осуществляется сигналом  на такте

на такте  . На рис. 7.3 приведена схема записи слова состояния с помощью схемы многорежимного буферного регистра К589ИР12.

. На рис. 7.3 приведена схема записи слова состояния с помощью схемы многорежимного буферного регистра К589ИР12.

Рассмотрим временные диаграммы работы микро-ЭВМ при различных машинных циклах.

Извлечение кода команды, данных из памяти или внешнего устройства. Цикл  является основным циклом, с которого начинается выполнение любой команды, поэтому временные процессы для него рассмотрим более подробно. Анализ процессов будем проводить по каждому машинному такту Т.

является основным циклом, с которого начинается выполнение любой команды, поэтому временные процессы для него рассмотрим более подробно. Анализ процессов будем проводить по каждому машинному такту Т.

На такте  (рис. 7.4) программный счетчик МП БИС выдает на МА адрес ячейки памяти, из которой будет считываться код команды. При этом схема приращения адреса МП БИС автоматически увеличивает на единицу значение числа, записанного в программном счетчике. Положительным фронтом сигнала

(рис. 7.4) программный счетчик МП БИС выдает на МА адрес ячейки памяти, из которой будет считываться код команды. При этом схема приращения адреса МП БИС автоматически увеличивает на единицу значение числа, записанного в программном счетчике. Положительным фронтом сигнала  формируется сигнал СИНХР и выдается слово состояния на МД. Сигнал ПРИЕМ, управляющий двунаправленным шинным формирователем (ДШФ) МД, на этом такте равен нулю, что позволяет слову состояния поступить на МД микро-ЭВМ.

формируется сигнал СИНХР и выдается слово состояния на МД. Сигнал ПРИЕМ, управляющий двунаправленным шинным формирователем (ДШФ) МД, на этом такте равен нулю, что позволяет слову состояния поступить на МД микро-ЭВМ.

На такте  слово состояния записывается в регистр. Положительным фронтом

слово состояния записывается в регистр. Положительным фронтом  заканчивается сигнал СИНХР и формируется единичный сигнал ПРИЕМ, позволяющий данным поступить на вход МП БИС через двунаправленный шинный формирователь. На такте

заканчивается сигнал СИНХР и формируется единичный сигнал ПРИЕМ, позволяющий данным поступить на вход МП БИС через двунаправленный шинный формирователь. На такте  из сигнала ПРИЕМ и седьмого разряда слова состояния (

из сигнала ПРИЕМ и седьмого разряда слова состояния (  ) формируется сигнал на чтение данных из памяти (Чт. ПАМЯТЬ), позволяющий данным поступать из памяти на МД (рис. 7.5). Изменения данных на этом такте восприниматься МП БИС не будут, так как их запись осуществляется в фиксированные моменты времени на такте

) формируется сигнал на чтение данных из памяти (Чт. ПАМЯТЬ), позволяющий данным поступать из памяти на МД (рис. 7.5). Изменения данных на этом такте восприниматься МП БИС не будут, так как их запись осуществляется в фиксированные моменты времени на такте  . На этом же такте анализируется состояние сигналов ГОТОВ, ЗАХВАТ и ОБ.ОСТ (см. рис. 7.4). При нулевом сигнале на входе З.ЗХ, в разряде

. На этом же такте анализируется состояние сигналов ГОТОВ, ЗАХВАТ и ОБ.ОСТ (см. рис. 7.4). При нулевом сигнале на входе З.ЗХ, в разряде  слова состояния и единичном сигнале на входе ГОТОВ МП БИС переходит к выполнению такта

слова состояния и единичном сигнале на входе ГОТОВ МП БИС переходит к выполнению такта  .

.

Если к моменту появления отрицательного фронта  на такте

на такте  сигнал на входе ГОТОВ будет иметь нулевой потенциал, то МП БИС на такте

сигнал на входе ГОТОВ будет иметь нулевой потенциал, то МП БИС на такте  переходит в режим ожидания. В этом режиме приостанавливается процесс обработки данных и формируется единичный сигнал на выходе ожидание, подтверждающий это состояние. Время ожидания выражается целым числом тактов и может длиться бесконечно долго. На каждом такте в этом режиме при отрицательном фронте

переходит в режим ожидания. В этом режиме приостанавливается процесс обработки данных и формируется единичный сигнал на выходе ожидание, подтверждающий это состояние. Время ожидания выражается целым числом тактов и может длиться бесконечно долго. На каждом такте в этом режиме при отрицательном фронте  будет проверяться состояние сигнала на входе ГОТОВ.

будет проверяться состояние сигнала на входе ГОТОВ.

Изменения в диаграммах работы МП БИС в режимах ЗАХВАТ, ОСТАНОВ и ПРЕРЫВАНИЕ будут рассмотрены отдельно.

На такте  в момент отрицательного фронта сигнала

в момент отрицательного фронта сигнала  производится запись данных во внутренний регистр кода команды. Положительным фронтом

производится запись данных во внутренний регистр кода команды. Положительным фронтом  оканчивается сигнал ПРИЕМ на выходе МП БИС и, следовательно, сигналы

оканчивается сигнал ПРИЕМ на выходе МП БИС и, следовательно, сигналы  . Отметим, что импульс на выходе ПРИЕМ будет формироваться МП БИС на машинных циклах: извлечения кода команды (

. Отметим, что импульс на выходе ПРИЕМ будет формироваться МП БИС на машинных циклах: извлечения кода команды (  ), чтения данных из памяти, прерывания, чтения из стека или внешнего устройства.

), чтения данных из памяти, прерывания, чтения из стека или внешнего устройства.

Рис. 7.3. Схема записи слова состояния в регистр слова состояния

На последующих тактах  и

и  дешифратор кода команды расшифровывает код команды, определяет количество байтов в команде, формирует команды на внутренние пересылки данных и подготавливает МП БИС к выполнению следующих машинных циклов. Отличие машинных циклов чтения данных из памяти, стека или ВУ по срав-нению с циклом

дешифратор кода команды расшифровывает код команды, определяет количество байтов в команде, формирует команды на внутренние пересылки данных и подготавливает МП БИС к выполнению следующих машинных циклов. Отличие машинных циклов чтения данных из памяти, стека или ВУ по срав-нению с циклом

Рис. 7.4. Временные диаграммы процесса получения МП БИС кода команды

будет заключаться лишь в том, что МП БИС будет воспринимать числа, полученные на такте  по МД не как код команды, а как данные. При записи данных с ВУ на МУ формируется сигнал чтения устройств ввода — вывода (

по МД не как код команды, а как данные. При записи данных с ВУ на МУ формируется сигнал чтения устройств ввода — вывода (  ) из сигнала ПРИЕМ и разряда

) из сигнала ПРИЕМ и разряда  слова состояния. Этот сигнал позволяет ВУ выдать информацию на МД микроЭВМ.

слова состояния. Этот сигнал позволяет ВУ выдать информацию на МД микроЭВМ.

Рис. 7.5. Схема чтения кода команды или данных из памяти

Запись данных в память или внешнее устройство. Процесс записи данных в память иллюстрируется на схеме, показанной на рис. 7.6, а, временные диаграммы — на рис. 7.6, б.

На такте  содержание регистра адреса МП БИС выдается на МА, а на МД выдается слово состояния.

содержание регистра адреса МП БИС выдается на МА, а на МД выдается слово состояния.

На такте  на МД выдаются данные для записи в память.

на МД выдаются данные для записи в память.

На такте  формируется сигнал, по которому будет проходить запись данных в память или ВУ-

формируется сигнал, по которому будет проходить запись данных в память или ВУ-

На протяжении всего машинного цикла записи данных в память сигнал ПРИЕМ находится на нулевом уровне, что позволяет двунаправленному

Рис. 7.6. (а) Схема записи данных в память

шинному формирователю работать в режиме выдачи данных на МД микроЭВМ.

Процесс записи данных во внешнее устройство аналогичен записи данных в память. Единственное отличие этого процесса заключается в формировании сигнала записи  . Для этого используется сигнал с выхода

. Для этого используется сигнал с выхода  и разряд

и разряд  слова состояния.

слова состояния.

Работа в режиме ЗАХВАТ. Режим ЗАХВАТ используется для останова управления МП БИС работой микро-ЭВМ. При работе в этом режиме выходные магистрали МП БИС переводятся в третье состояние и отключаются от магистралей микро-ЭВМ, обеспечивая тем самым возможность обмена информацией с микроЭВМ по каналу прямого доступа к памяти. Режим ЗАХВАТ инициируется подачей сигнала «1» на вход управления З.ЗХ МП БИС подтверждает переход в режим ЗАХВАТ путем

б)

Рис. 7.6. (б). Временные диаграммы процесса

выдачи сигнала «1» на выходе П.ЗХ. Состояние ЗАХВАТ будет длиться целое число тактов. Установка низкого уровня потенциала на входе З.ЗХ проверяется на каждом сигнале  , и при его наличии на следующем импульсе режим захвата будет прекращен и МП

, и при его наличии на следующем импульсе режим захвата будет прекращен и МП

БИС перейдет к выполнению очередного машинного цикла начиная с такта  .

.

Работа при выполнении команды HALT. Режим ОСТАНОВ является результатом выполнения команды HALT. Находясь в этом режиме, магистрали МП БИС не отключаются от магистралей микро-ЭВМ, а процессор просто отмечает время, в течение которого он ничего не выполняет. Состояние микро-ЭВМ в этом режиме аналогично состоянию ОЖИДАНИЕ, за исключением того, что это состояние устанавливается программно.

Обычно режим ОСТАНОВ оканчивается тогда, когда ВУ выдают запрос на обслуживание. Один из методов формирования запроса на обслуживание — подача запроса прерывания на вход З.Пр МП БИС (уровень «1» на входе 3. Пр).

Если сигналы прерывания не воспринимаются МП БИС (например, после выполнения команды DI), то остается один выход из состояния ОСТАНОВ—подача сигнала начальной установки на вход R МП БИС.

Специфика режима ОСТАНОВ заключается в том, что в этом состоянии МП БИС может входить в режим ЗАХВАТ и выходить из него. В режиме ОСТАНОВ запрос на ЗАХВАТ не будет удовлетворяться, если запрос на прерывание был уже подан на вход З.Пр, но не было еще подтверждено его обслуживание (уровень «1» на выходе П.Пр не установлен). После подтверждения получения прерывания (уровень «0» на выходе П.Пр) микро-ЭВМ может войти в состояние ЗАХВАТ.

Обслуживание запросов на прерывание. Внешние устройства выдают сигнал запроса прерывания асинхронно по отношению к работе МП БИС путем подачи уровня «1» на вход З.Пр. Запрос может быть удовлетворен только в том случае, если МП БИС находится в состоянии разрешения восприятия запросов прерывания. МП БИС автоматически устанавливается в состояние запрета восприятия запросов прерывания после выполнения начальной установки, а также после начала обслуживания запроса прерывания. Управление состоянием восприятия запросов прерывания может осуществляться программно с помощью команд: EI—«Разрешение прерываний» и DI—«Запрет прерываний».

МП БИС указывает на возможность восприятия прерываний на выходе Р.Пр. Если на этом выходе присутствует уровень «1», то запросы прерывания могут быть восприняты, в противном случае (уровень «0» на выходе Р.Пр) запросы восприниматься не будут.

Если запрос прерывания воспринят, то начинается цикл обслуживания прерывания. На первом машинном цикле обслуживания прерывания МП БИС получает по МД микро-ЭВМ код прерывания. Имеется два способа задания кода прерывания: с помощью команды RSТ <N> и с помощью команды CALL<  > <

> <  > (векторный способ). Первый цикл для обоих способов является общим и отличается от цикла

> (векторный способ). Первый цикл для обоих способов является общим и отличается от цикла  извлечения кода команды из памяти тем, что содержание программного счетчика МП БИС при этом увеличивается. На первом такте

извлечения кода команды из памяти тем, что содержание программного счетчика МП БИС при этом увеличивается. На первом такте  устанавливается уровень «0» на выходе Р. Пр. МП БИС информирует ВУ о восприятии и начале обслуживания прерывания выдачей слова состояния с «1» в разрядах

устанавливается уровень «0» на выходе Р. Пр. МП БИС информирует ВУ о восприятии и начале обслуживания прерывания выдачей слова состояния с «1» в разрядах  ,

,  ,

,  . Разряд

. Разряд  совместно с сигналом на выходе ПРИЕМ используется для формирования сигнала

совместно с сигналом на выходе ПРИЕМ используется для формирования сигнала  (обслуживание прерывания) магистрали управления микро-ЭВМ (рис. 7.7). По этому сигналу ВУ выдают на МД микро-ЭВМ либо код команды RSТ<N> , либо код команды САLL <

(обслуживание прерывания) магистрали управления микро-ЭВМ (рис. 7.7). По этому сигналу ВУ выдают на МД микро-ЭВМ либо код команды RSТ<N> , либо код команды САLL <  > <

> <  >.

>.

Существует восемь кодов команды RST<N> , где N = 0 : 7. Команда RSТ<N> указывает начальный адрес подпрограммы обслуживания прерывания. Получив команду на первом машинном цикле, МП БИС на циклах  и

и  записывает в область памяти, отведенной под стек, текущее значение программного счетчика РС. Сохранение содержания РС в стеке необходимо для возврата к прерванной программе после окончания выполнения подпрограммы обслуживания прерывания. Возврат можно осуществить с помощью команды RET (RETURN), которая загружает содержание двух верхних ячеек стека в РС. Таким образом, каждая подпрограмма обслуживания прерываний должна в конце иметь команду RET.

записывает в область памяти, отведенной под стек, текущее значение программного счетчика РС. Сохранение содержания РС в стеке необходимо для возврата к прерванной программе после окончания выполнения подпрограммы обслуживания прерывания. Возврат можно осуществить с помощью команды RET (RETURN), которая загружает содержание двух верхних ячеек стека в РС. Таким образом, каждая подпрограмма обслуживания прерываний должна в конце иметь команду RET.

Первым машинным циклом при обращении к ячейкам памяти, указанным в команде RST<N>, является цикл  извлечения команды.

извлечения команды.

При векторном способе задания прерываний на первом цикле  ВУ будет передавать МП БИС не команду RST<N>, а команду CALL<

ВУ будет передавать МП БИС не команду RST<N>, а команду CALL<  > <

> <  > . Получив команду САLL, МП БИС автоматически переходит в режим ввода 2 байт адреса

> . Получив команду САLL, МП БИС автоматически переходит в режим ввода 2 байт адреса  и

и  на циклах

на циклах  ,

,  . После этого организуется сохранение содержания РС в стеке и обращение к началу подпрограммы обслуживания прерывания. Начало подпрограммы указано во втором и третьем байтах (<

. После этого организуется сохранение содержания РС в стеке и обращение к началу подпрограммы обслуживания прерывания. Начало подпрограммы указано во втором и третьем байтах (<  > <

> <  >) команды САLL. Отметим, что при векторном способе задания прерывания ВУ сообщает не только команду CALL, но и адрес начала подпрограммы обслуживания прерываний.

>) команды САLL. Отметим, что при векторном способе задания прерывания ВУ сообщает не только команду CALL, но и адрес начала подпрограммы обслуживания прерываний.

Начальная установка. В течение всего времени, пока на входе R установлен уровень «1», все операции в МП БИС будут приостановлены. За это время обнуляются программный счетчик, триггер разрешения прерываний и внутренняя логика, связанная с формированием сигнала П.ЗХ. Так как программный счетчик содержит к этому времени число 0000, то первая выполняемая команда будет записана по адресу 0000.

Прерывания остаются отключенными после начала выполнения программы, и для восстановления возможности восприятия запросов прерывания в программу необходимо включать команду EI—«Разрешение прерываний».

Организация магистралей микро-ЭВМ. Обмен информацией между МП БИС и ВУ организуется с помощью трех магистралей микро-ЭВМ: МА, МД и МУ. Ввиду малой нагрузочной способности, а также ограниченного числа выводов МП БИС в микро-ЭВМ необходимо использовать дополнительные схемы для организации этих магистралей.

Магистраль адресов является однонаправленной магистралью, выдача адресов на которую осуществляется лишь МП БИС или схемой прямого доступа к памяти при работе микро-ЭВМ с каналом прямого доступа к памяти, Малая нагрузочная способность МА требует применения буфера.

По МД организуется двунаправленный обмен данными между МП БИС и

Рис. 7.7. Ввод кода команды RST1 при обслуживании МП БИС

сигнала прерывания

памятью или ВУ. Максимальная нагрузочная способность МД невелика, что не позволяет непосредственно подключать к ней системы с большой емкостью памяти и широким набором периферийных устройств. Для увеличения нагрузочной способности МД микро-ЭВМ необходимо также применять буфер МД.

Магистраль управления состоит из пяти шин, сигналы на которых формируются из записанного слова состояния МП БИС и его выходных сигналов ПРИЕМ и  . На рис. 7.8 приведены организации МУ на схеме КР580ВН28*

. На рис. 7.8 приведены организации МУ на схеме КР580ВН28*

Команды МП БИС КР580ВМ80. Восьмиразрядное машинное слово используется для сообщения МП БИС как кода команд, так и данных. Набор команд фиксирован и состоит из 246 различных команд [12]. Все команды можно разделить на пять групп: 1. Команды переноса данных, осуществляющие перенос данных между регистрами или между регистрами и памятью. 2. Арифметические команды, включающие в себя команды сложения, вычитания, увеличения или уменьшения на единицу данных в регистрах или памяти. 3- Логические команды, позволяющие осуществить логические операции И, ИЛИ, исключающее ИЛИ, сравнение, сдвиг или взятие дополнения числа в регистрах или памяти. 4. Команды передачи управления, обеспечивающие безусловную или передачу управления по условию, а также вызов или возврат из подпрограмм. 5. Команды управления и работы со стеком, организующие ввод— вывод данных из микроЭВМ, доступ к стеку и внутреннему регистру признаков МП БИС, а также ее управление.

Память микро-ЭВМ организована в виде 8-разрядных ячеек, каждая из которых имеет свой 16-разрядный адрес. Таким образом, МП БИС может работать с памятью емкостью до 65 536 байт. Одна команда может содержать от 1 до 3 байт. Многобайтовые команды записываются в последовательные ячейки памяти. Первый байт команды всегда содержит код команды. При трехбайтовых командах во втором и третьем байтах содержатся данные (адрес), причем во втором байте записывается младший байт данных, а в третьем—старший байт данных (адреса).

МП БИС имеет четыре различных типа адресации к памяти или регистрам: 1. Прямая адресация—второй и третий байты команды содержат указание адреса памяти (младший байт адреса во втором байте команды, а старший байт—в третьем). 2. Адресация к регистру— команда указывает на регистр или пару регистров, в которых записаны данные. 3. Косвенная адресация с помощью регистров—команда указывает на пару регистров в которых записан адрес памяти или данные. 4. Непосредственная—команда сама содержит данные. При двухбайтовых данных во втором байте команды записывается младший байт, а в третьем—старший.

За исключением обслуживания и прерываний и выполнения команд передачи управления, МП БИС осуществляет выполнение программы, считывая команды последовательно из ячеек памяти.

В командах передачи управления адрес, к которому будет обращаться МП БИС, может указываться с помощью прямой или косвенной адресации. При выполнении команд передачи управления по условию МП БИС проверяет наличие условия и в случае его подтверждения осуществляет передачу управления. При неудовлетворении условия выполнение программы будет продолжаться с команды, записанной в ячейке памяти, следующей после команды передачи управления по условию. При обслуживании прерывания в зависимости от кода команды RST<N> МП БИС обращается к одной из восьми фиксированных ячеек памяти. Полный перечень команд МП БИС КР580ВМ80 приведен в табл. 7.1.

Рис. 7.8. Схема формирования МУ микро-ЭВМ.

Таблица 7.1

| Код | Мнемоника | Код | Мнемоника | Код | Мнемоника | Код | Мнемоника | Код | Мнемоника | Код | Мнемоника |

| NOP | - | MOV H, B | SUB В | С0 | RNZ | F0 | RР | ||||

| LXI B, D16 | LXI SP, D16 | MOV H, C | SUB C | С1 | РОРВ | F1 | РОР PSW Р51У | ||||

| SТАХ В | STA Adr | MOV H, D | SUB D | С2 | JNZ Adr | F2 | JP Adr | ||||

| INX B | INX SP | MOV H, E | SUB E | СЗ | JMP Adr | F3 | D1 | ||||

| INR В | INR M | MOV H, Н | SUB H | С4 | CNZ Adr | F4 | СР Adr | ||||

| DCR В | DCR М | MOV H, L | SUB L | С5 | PYSH В | F5 | PUSH PSW | ||||

| MVI B, D8 | MVI M, D8 | MOV Н, М | SUB M | С6 | АDI, D8 | F6 | ОRI, D8 | ||||

| RLC | STC | МОV Н, А | SUB A | С7 | RST 0 | F7 | RST 6 | ||||

| - | - | МОV L, В | SBB B | С8 | RZ | F8 | RМ | ||||

| DАD В | DAD, SP | MOV L, C | SВВ С | С9 | RЕТ | F9 | SРНL | ||||

ОА ОА

| LDАХ В | ЗA | LDA Adr | 6A | МОV L, D | 9Л | SВВ D | СА | JZ Adr | FA | JM Adr |

| ОВ | DСХ В | 3B | DСХ SР | 6B | МОV L, Е | 9B | SВВ Е | СВ | - | FВ | EI |

| ОС | INR C | ЗС | INR A | 6С | МОV L, Н | 9С | SВВ Н | CC | СZ Adr | FС | CM Adr |

| OD | DCR C | 3D | DСR А | 6D | МОV L, L | 9D | SВВ L | CD | САLL Adr | FD | - |

| ОЕ | MVI C, D8 | ЗE | МVI A, D8 | 6Е | МОV L, М | 9Е | SВВ М | СЕ | АСI D8 | FЕ | CPI, D8 |

| ОF | RRC | ЗF | СМC | 6F | МОV L, А | 9F | SВВ А | СF | RST 1 | FF | RSТ 7 |

| - | МОV В, В | МОV М, В | A0 | ANA B | D0 | RNC | |||||

| LXI D, D16 | МОV B, С | МОV М, С | А1 | ANA С | D1 | РОР D | |||||

| SТАХ D | МОV В, D | МОV M, D | A2 | ANA D | D2 | JNC Adr | |||||

| INX D | МОV В, Е | МОV М, Е | AЗ | ANA E | D3 | OUT D8 | |||||

| INR D | МОV В, H | МОV М, Н | A4 | ANA Н | D4 | CNC Adr | |||||

| DСR D | MOV B, L | МОV М, L | A5 | ANA L | D5 | РUSН D | |||||

| MVI D, D8 | МОV В, М | HLT | A6 | ANA М. | D6 | SUI D8 | |||||

| RAL | МОV В, А | МОV М, А | A7 | ANA А | D7 | RSТ 2 | |||||

| - | МОV С, В | МОV А, В | A8 | ХRА В | D8 | RС |

Продолжение табл.7.1

| Код | Мнемоника | Код | Мнемоника | Код | Мнемоника | Код | Мнемоника | Код | Мнемоника | Код | Мнемоника |

| DАD D | МОV С, С | МОV А, С | A9 | ХRА С | D9 | - | |||||

| 1A | LDАХ D | 4A | МОV С, D | 7A | МОV А, D | AА | ХRА D | DA | JC Adr | ||

| 1B | DСХ D | 4B | МОV С, Е | 7B | МОV А, Е | AB | ХRА Е | DB | IN, D8 | ||

| 1С | INR E | 4С |

Дата добавления: 2016-06-05; просмотров: 2769;