Error Frame, Overload Frame

Data Frame - это наиболее часто используемый тип сообщения. Он состоит из следующих основных частей: "Начало кадра", "поле арбитража", "поле контроля", "поле данных", "поле CRC", "поле подтверждения", "конец кадра".

Каждая часть имеет определенный формат

Remote Frame - это Data Frame без поля данных и с выставленным битом RTR. Основное предназначение Remote кадра - это инициация одним из узлов сети передачи в сеть данных другим узлом, запрос определенного сообщения.

Error Frame - это сообщение которое явно нарушает формат сообщения CAN. Передача такого сообщения приводит к тому, что все узлы сети регистрируют ошибку формата CAN-кадра, и в свою очередь автоматически передают в сеть Error Frame. Результатом этого процесса является автоматическая повторная передача данных в сеть передающим узлом.

Overload Frame - Имеются два вида перегрузки, которые оба приводят к передаче кадра перегрузки.

1. Внутреннее состояние приёмника, которое требует задержки следующего кадра данных или кадра удаленного запроса данных.

2. Обнаружение бита с лог. "0" в течение поля перерыва в межкадровом пространстве.

Передача кадра перегрузки из-за состояния 1 возможна только в первом битовом интервале перерыва, в то время как кадры перегрузки по состоянию 2 начинают передаваться на следующем битовом интервале после обнаружения бита с лог. "0".

Для больших задержек может быть послано несколько кадров перегрузки.

I2C

Каждый, кто занимался разработкой радиоэлектронной техники, сталкивался с ситуацией, когда для согласования уровней сигналов, выборки и адресации функционально-законченных узлов, приходится использовать огромное количество промежуточных ИС.

Для увеличения эффективности, упрощения схемотехнических решений, Philips разработала простую двунаправленную двухпроводную шину для так называемого "межмикросхемного" (inter-IC) управления.

Шина получила название - InterIC, или IIC (I2C) шина.

В настоящее время только Philips производит более 150 наименований I2C-совместимых устройств, функционально предназначенных работы в электронном оборудовании различного назначения. В их числе ИС памяти, видеопроцессоров и модулей обработки аудио- и видео-сигналов, АЦП и ЦАП, драйверы ЖК-индикаторов, процессоры со встроенным аппаратным контроллером I2C шины и многое другое.

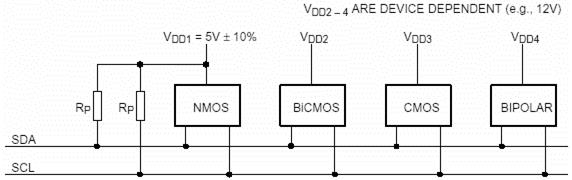

I2C шина является одной из модификаций последовательных протоколов обмена данных. В стандартном режиме обеспечивается передача последовательных 8-битных данных со скоростью до 100 кбит/с, и до 400 кбит/с в "быстром" режиме. Для осуществления процесса обмена информацией по I2C шине, используется всего два сигнала линия данных SDA линия синхронизации SCL. Для обеспечения реализации двунаправленности шины без применения сложных арбитров шины выходные каскады устройств, подключенных к шине, имеют открытый сток или открытый коллектор для обеспечения функции монтажного "И".

Максимальное допустимое количество микросхем, подсоединённых к одной шине, ограничивается максимальной емкостью шины 400 пФ.

Все I2C-совместимые устройства имеют интерфейс, который позволяет им связываться друг с другом по шине даже в том случае, если их напряжение питания существенно отличается. На следующем рисунке представлен принцип подключения нескольких ИМС с различными напряжениями питания к одной шине обмена.

Рисунок_6.15 Архитектура шины I2C.

Каждое устройство распознается по уникальному адресу и может работать как передатчик или приёмник, в зависимости от назначения устройства.

Кроме того, устройства могут быть классифицированы как ведущие и ведомые при передаче данных. Ведущий - это устройство, которое инициирует передачу данных и вырабатывает сигналы синхронизации. При этом любое адресуемое устройство считается ведомым по отношению к ведущему.

Исходя из спецификации работы шины, в каждый отдельный момент в шине может быть только один ведущий, а именно то устройство, которое обеспечивает формирование сигнала SCL шины. Ведущий может выступать как в роли ведущего-передатчика, так и ведущего-приемника. Тем не менее - шина позволяет иметь несколько ведущих, накладывая определенные особенности их поведения в формировании сигналов управления и контроля состояния шины. Возможность подключения более одного ведущего к шине означает, что более чем один ведущий может попытаться начать пересылку в один и тот же момент времени. Для устранения "столкновений", который может возникнуть в данном случае, разработана процедура арбитража - поведения ведущего при обнаружении "захвата" шины другим ведущим.

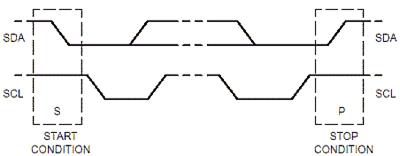

Состояние СТАРТ и СТОП

Процедура обмена начинается с того, что ведущий формирует состояние СТАРТ - ведущий генерирует переход сигнала линии SDA из ВЫСОКОГО состояния в НИЗКОЕ при ВЫСОКОМ уровне на линии SCL. Этот переход воспринимается всеми устройствами, подключенными к шине как признак начала процедуры обмена.

Рисунок 6.16 Старт и стоп условия

Генерация синхросигнала - это всегда обязанность ведущего; каждый ведущий генерирует свой собственный сигнал синхронизации при пересылке данных по шине.

Процедура обмена завершается тем, что ведущий формирует состояние СТОП - переход состояния линии SDA из низкого состояния в ВЫСОКОЕ при ВЫСОКОМ состоянии линии SCL.

Состояния СТАРТ и СТОП всегда вырабатываются ведущим. Считается, что шина занята после фиксации состояния СТАРТ. Шина считается освободившейся через некоторое время после фиксации состояния СТОП.

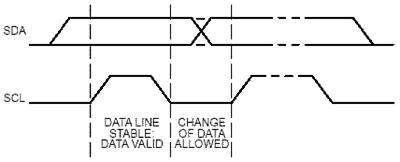

Рисунок 6.17- Передача одного бита

При передаче посылок по шине I2C каждый ведущий генерирует свой синхросигнал на линии SCL.

После формирования состояния СТАРТ, ведущий опускает состояние линии SCL в НИЗКОЕ состояние и выставляет на линию SDA старший бит первого байта сообщения. Количество байт в сообщении не ограничено.

Спецификация шины I2C разрешает изменения на линии SDA только при НИЗКОМ уровне сигнала на линии SCL.

Данные действительны и должны оставаться стабильными только во время ВЫСОКОГО состояния синхроимпульса.

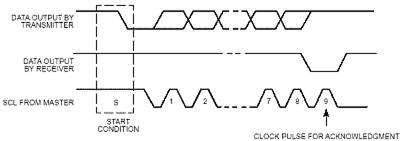

Для подтверждения приема байта от ведущего - передатчика ведомым - приемником в спецификации протокола обмена по шине I2C вводится специальный бит подтверждения, выставляемый на шину SDA после приема 8 бита данных.

Подтверждение

Таким образом передача 8 бит данных от передатчика к приемнику завершаются дополнительным циклом (формированием 9-го тактового импульса линии SCL), при котором приемник выставляет низкий уровень сигнала на линии SDA, как признак успешного приема байта.

Рисунок 6.18 Передача 8 бит

Подтверждение при передаче данных обязательно. Соответствующий импульс синхронизации генерируется ведущим. Передатчик отпускает (ВЫСОКОЕ) линию SDA на время синхроимпульса подтверждения. Приёмник должен удерживать линию SDA в течение ВЫСОКОГО состояния синхроимпульса подтверждения в стабильном НИЗКОМ состоянии.

В том случае, когда ведомый-приёмник не может подтвердить свой адрес (например, когда он выполняет в данный момент какие-либо функции реального времени), линия данных должна быть оставлена в ВЫСОКОМ состоянии. После этого ведущий может выдать сигнал СТОП для прерывания пересылки данных.

Если в пересылке участвует ведущий-приёмник, то он должен сообщить об окончании передачи ведомому-передатчику путем не подтверждения последнего байта. Ведомый-передатчик должен освободить линию данных для того, чтобы позволить ведущему выдать сигнал СТОП или повторить сигнал СТАРТ.

Синхронизация выполняется с использованием подключения к линии SCL по правилу монтажного И.

Это означает, что ведущий не имеет монопольного права на управление переходом линии SCL из НИЗКОГО состояния ВЫСОКОГО. В том случае, когда ведомому необходимо дополнительное время на обработку принятого бита, он имеет возможность удерживать линию SCL в низком состоянии до момента готовности к приему следующего бита. Таким образом, линия SCL будет находиться в НИЗКОМ состоянии на протяжении самого длинного НИЗКОГО периода синхросигналов.

Устройства с более коротким НИЗКИМ периодом будут входить в состояние ожидания на время, пока не кончится длинный период. Когда у всех задействованных устройств кончится НИЗКИЙ период синхросигнала, линия SCL перейдет в ВЫСОКОЕ состояние. Все устройства начнут проходить ВЫСОКИЙ период своих синхросигналов. Первое устройство, у которого кончится этот период, снова установит линию SCL в НИЗКОЕ состояние. Таким образом, НИЗКИЙ период синхролинии SCL определяется наидлиннейшим периодом синхронизации из всех задействованных устройств, а ВЫСОКИЙ период определяется самым коротким периодом синхронизации устройств.

Механизм синхронизации может быть использован приемниками как средство управления пересылкой данных на байтовом и битовом уровнях.

На уровне байта, если устройство может принимать байты данных с большой скоростью, но требует определенное время для сохранения принятого байта или подготовки к приему следующего, то оно может удерживать линию SCL в НИЗКОМ состоянии после приема и подтверждения байта, переводя таким образом передатчик в состояние ожидания.

На уровне битов, устройство такое как микроконтроллер без встроенных аппаратных цепей I2C или с ограниченными цепями может замедлить частоту синхроимпульсов путем продления их НИЗКОГО периода. Таким образом скорость передачи любого ведущего адаптируется к скорости медленного устройства.

Адресация в шине I2C

Каждое устройство, подключённое к шине, может быть программно адресовано по уникальному адресу.

Для выбора приемника сообщения ведущий использует уникальный адресную компоненту в формате посылки. При использовании однотипных устройств, ИС часто имеют дополнительный селектор адреса, который может быть реализован как в виде дополнительных цифровых входов селектора адреса, так и в виде аналогового входа. При этом адреса таких однотипных устройств оказываются разнесены в адресном пространстве устройств, подключенных к шине.

В обычном режиме используется 7-битная адресация.

Процедура адресации на шине I2C заключается в том, что первый байт после сигнала СТАРТ определяет, какой ведомый адресуется ведущим для проведения цикла обмена. Исключение составляет адрес "Общего вызова", который адресует все устройства на шине. Когда используется этот адрес, все устройства в теории должны послать сигнал подтверждения. Однако, устройства могут обрабатывать "общий вызов" на практике встречаются редко.

Первые семь битов первого байта образуют адрес ведомого. Восьмой, младший бит, определяет направление пересылки данных. "Ноль" означает, что ведущий будет записывать информацию в выбранного ведомого. "Единица" означает, что ведущий будет считывать информацию из ведомого.

После того, как адрес послан, каждое устройство в системе сравнивает первые семь бит после сигнала СТАРТ со своим адресом. При совпадении устройство полагает себя выбранным как ведомый-приёмник или как ведомый-передатчик, в зависимости от бита направления.

Адрес ведомого может состоять из фиксированной и программируемой части.

Часто случается, что в системе будет несколько однотипных устройств (к примеру ИМС памяти, или драйверов LED-индикаторов), поэтому при помощи программируемой части адреса становится возможным подключить к шине максимально возможное количество таких устройств. Количество программируемых бит в адресе зависит от количества свободных выводов микросхемы. Иногда используется один вывод с аналоговой установкой программируемого диапазона адресов, как это, к примеру, реализовано в ИМС SAA1064. При этом в зависимости от потенциала на этом адресном выводе ИМС, возможно смещение адресного пространства драйвера так, чтобы однотипные ИМС не конфликтовали между собой на общей шине.

Все ИМС, поддерживающие работу в стандарте шины I2C, имеют набор фиксированых адресов, перечень которых указан производителем в описаниях контроллеров.

Комбинация бит 11110ХХ адреса зарезервирована для 10-битной адресации.

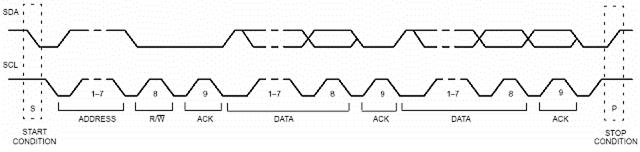

В общем виде процесс обмена по шине от момента формирования состояния СТАРТ до состояния СТОП можно проиллюстрировать следующим рисунком :

Рисунок 6.19 Передача нескольких байт по шине I2C.

Как следует из спецификации шины, допускаются как простые форматы обмена, так и комбинированные, когда в промежутке от состояния СТАРТ до состояния СТОП ведущий и ведомый могут выступать и как приемник и как передатчик данных. Комбинированные форматы могут быть использованы, например, для управления последовательной памятью.

Во время первого байта данных можно передавать адрес в памяти, который записывается во внутренний регистр-защелку. После повторения сигнала СТАРТа и адреса ведомого выдаются данные из памяти. Все решения об авто-инкременте или декременте адреса, к которому произошел предыдущий доступ, принимаются конструктором конкретного устройства. Поэтому, в любом случае лучший способ избежать неконтролируемой ситуации на шине перед использованием новой (или ранее не используемой) ИМС следует тщательно изучить ее описание (datasheet), получив его с сайта производителя. Более того, производители часто размещают рядом более подробные инструкции по применению.

В любом случае, по спецификации шины все разрабатываемые устройства должны сбрасывать логику шины при получении сигнала СТАРТ или повторный СТАРТ и подготавливаться к приему адреса.

Тем не менее основные проблемы с использованием I2C шины возникают именно из-за того, что разработчики, "начинающие" работать с I2C шиной не учитывают того факта, что ведущий (часто - микропроцессор) не имеет монопольного права ни на одну из линий шины.

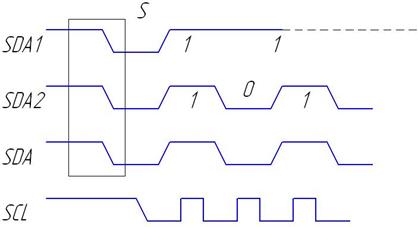

Арбитраж.

Мастер может начинать передачу только если шина свободна. Два и более мастера могут генерировать в состояние START почти одновременно. Следовательно, необходим арбитраж между ними для того, чтобы выяснить кто передаст свои данные. Для этого используется линия SDA. Она так же, как SCL выполнена по схеме монтажной &. Рассмотрим процедуру арбитража:

Рисунок 6.20 Арбитраж.

Как видно из рисунка, если данные, передаваемые мастером, не соответствуют состоянию шины, например, на втором такте состояние шины SDA не соответствует состоянию шины SDA1 поэтому передатчик автоматически отключается от шины (SDA1=1).

SPI

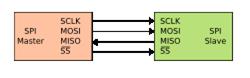

SPI (англ. Serial Peripheral Interface, SPI bus — последовательный периферийный интерфейс, шина SPI) — последовательный синхронный стандарт передачи данных в режиме полного дуплекса, разработанный компанией Motorola для обеспечения простого и недорогого сопряжения микроконтроллеров и периферии. SPI также иногда называют четырёхпроводным (англ. four-wire) интерфейсом .

В отличие от стандартного последовательного порта (standard serial port), SPI является синхронным протоколом, в котором любая передача синхронизирована с общим тактовым сигналом, генерируемым ведущим устройством (процессором). Принимающая периферия (ведомая) синхронизирует получение битовой последовательности с тактовым сигналом. К одному последовательному периферийному интерфейсу ведущего устройства-микросхемы может присоединяться несколько микросхем. Ведущее устройство выбирает ведомое для передачи, активируя сигнал «выбор кристалла» (chip select) на ведомой микросхеме. Периферия, не выбранная процессором, не принимает участие в передаче по SPI.

Рисунок 6.21 Организация шины SPI

В SPI используются четыре цифровых сигнала:

MOSI или SI — выход ведущего, вход ведомого (англ. Master Out Slave In). Служит для передачи данных от ведущего устройства ведомому.

MISO или SO — вход ведущего, выход ведомого (англ. Master In Slave Out). Служит для передачи данных от ведомого устройства ведущему.

SCLK или SCK — последовательный тактовый сигнал (англ. Serial CLocK). Служит для передачи тактового сигнала для ведомых устройств.

CS или SS — выбор микросхемы, выбор ведомого (англ. Chip Select, Slave Select).

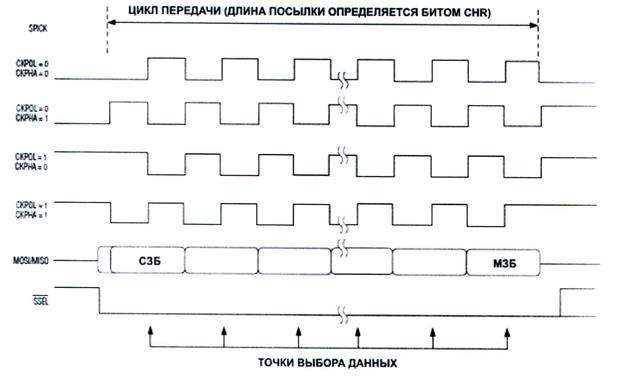

В течении передачи по интерфейсу SPI даны одновременно передаются и принимаются по двум линиям синхронно с синхроимпульсом. Полярность и фаза последовательных синхроимпульсов – это основной компонент, определяющий формат передачи данных по интерфейсу SPI. Полярность последовательных синхроимпульсов соответствует свободному состоянию линий синхронизации SCK. Фаза синхроимпульсов определяет, по какому фронту (активному или неактивному) будет осуществляться захват данных. Если логическое состояние свободной линии синхронизации определено как низкое, то активным фронтом синхроимпульса является переход от низкого к высокому, а неактивным – от высокого к низкому. Полярность и фазу можно определить с помощью двух бит, в разных реализациях они называются по разному или реализован только один из вариантов. Обозначив эти биты CKPOL и CKPHA, рассмотрим форматы передачи:

Рисунок 6.22 возможные форматы передачи по интерфейсу SPI.

WIRE

Www.radiokot.ru

Www.gaw.ru

Интерфейс 1-Wire разработан фирмой Dallas Semiconductor. Документация по указанному интерфейсу и устройствах, его поддерживающих, находится по адресу http://www.maxim-ic.com/1-Wire.cfm.

Данный интерфейс по одной линии позволяет осуществлять ввод вывод информации. Протокол обмена по этому интерфейсу очень прост и легко реализуется программно практически на любых МК, есть и специальные микросхемы-адаптеры.

Рисунок 6.24 схема аппаратной реализации интерфейса 1-Wire.

Вывод DQ устройства представляет собой вход КМОП-логического элемента, который может быть зашунтирован (замкнут на общий провод) полевым транзистором. Сопротивление канала этого транзистора в открытом состоянии - около 100 Ом. Когда транзистор заперт - имеется небольшой ток утечки (примерно 5 мкА) на общий провод.

Шина 1-Wire должна быть подтянута отдельным резистором к напряжению питания устройств (которое, кстати, может быть от 3 до 5В- уточняется по характеристикам конкретного устройства). Сопротивление этого резистора 4.7 К, однако, это значение рекомендовано только для достаточно коротких линий. Если шина 1-Wire используется для подключения удаленных на большое расстояние устройств, то сопротивление этого резистора следует уменьшить. Минимально допустимое его сопротивление - около 300 Ом, а максимальное - около пары-тройки десятков килоом.

Подключение шины 1-Wire к МК показано условно в двух вариантах: с использованием 2 отдельных выводов МК (один в качестве выхода, а другой в качестве входа), так и одного, работающего и на ввод и на вывод. Разделение этих способов показано пунктирной линией, условно обозначающей границу корпуса МК. С некоторой натяжкой можно представить себе логическое строение шины 1-Wire как всем известное соединение выводов микросхем с открытым коллектором по схеме "монтажное И". Очевидно, что передача какой-либо информации при этом возможна только выдачей низкого уровня в линию, т.е. замыканием ее на общий провод, а в высокий логический уровень линия вернется сама, благодаря наличию внешнего подтягивающего резистора. Так же очевидно, что одновременная передача нескольких устройств обречена на неудачу из-за полного искажения информации (все передаваемые единицы одного устройства будут подавлены передаваемыми нулями от другого устройства).

Рассмотрим обмен информацией по шине 1-Wire.

1. Обмен всегда ведется по инициативе одного ведущего устройства, которое в большинстве случаев является микроконтроллером (МК).

2. Любой обмен информацией начинается с подачи импульса сброса ("Reset Pulse" или просто RESET) в линию 1-Wire ведущим устройством.

3. Для интерфейса 1-Wire в общем случае предусматривается "горячее" подключение и отключение устройств.

4. Любое устройство, подключенное к 1-Wire после получения питания выдает в линию DQ импульс присутствия, называемый "Presence pulse" (далее я буду использовать термин PRESENCE). Этот же импульс устройство всегда выдает в линию, если обнаружит сигнал RESET.

5. Появление в шине 1-Wire импульса PRESENCE после выдачи RESET однозначно свидетельствует о наличии хотя бы одного подключенного устройства.

6. Обмен информации ведется так называемыми тайм-слотами: один тайм-слот служит для обмена одним битом информации.

7. Данные передаются побайтно, бит за битом, начиная с младшего бита.

8. Достоверность переданных/принятых данных (проверка отсутствия искажений) гарантируется путем подсчета циклической контрольной суммы.

На следующем рисунке показана диаграмма сигналов RESET и PRESENCE, с которых всегда начинается любой обмен данными. Кстати, выдача импульса RESET в процессе обмена служит для досрочного завершения процедуры обмена информацией.

Рисунок 6.25 Временная диаграмма импульсов RESET и PRESENCE. Как видим, длительность большинства временных интервалов очень приблизительная и имеет только ограничение только по минимуму (не меньше указанного). Условные обозначения линий, показанные на Рис. 2, будут использоваться и далее.

Импульс RESET формирует ведущий МК, переводя в низкий логический уровень шину 1-Wire и удерживая ее в этом состоянии минимум 480 микросекунд. Затем МК должен "отпустить" шину. Через некоторое время, зависящее от емкости линии и сопротивления подтягивающего резистора, в линии установится высокий логический уровень. Протокол 1-Wire ограничивает это время "релаксации" диапазоном от 15 до 60 микросекунд, что и является определяющим для выбора подтягивающего резистора (как правило, емкость линии мы менять существенно не можем, а именно она оказывает существенное влияние на время возврата линии к высокому уровню).

Обнаружив импульс RESET, ведомое устройство приводит свои внутренние узлы в исходное состояние и формирует ответный импульс PRESENCE, как следует из рисунка - не позже 60 микросекунд после завершения импульса RESET. Для этого устройство переводит в низкий уровень линию DQ и удерживает ее в этом состоянии от 60 до 240 микросекунд. Конкретное время удержания зависит от многих параметров, но всегда находится в указанном диапазоне. После этого устройство так же "отпускает" шину.

После завершения импульса PRESENCE устройству дается еще некоторое время для завершения внутренних процедур инициализации, таким образом, МК должен приступить к любому обмену с устройством не ранее, чем через 480 микросекунд после завершения импульса RESET.

Итак, процедура инициализации интерфейса, с которой начинается любой обмен данными между устройствами, длится минимум 960 микросекунд, состоит из передачи от МК сигнала RESET и приему от устройства сигнала PRESENCE. Если сигнал PRESENCE не обнаружен - значит на шине 1-Wire нет готовых к обмену устройств.

Теперь рассмотрим процедуры обмена битами информации, которые, как вы помните, осуществляются определенными тайм-слотами. Тайм-слот - это по существу определенная, довольно жестко лимитированная по времени последовательность смены уровней сигнала в линии 1-Wire. Различают 4 типа тайм-слотов (я буду использовать термин МК, как синоним "ведущего устройства" и просто "устройство", как синоним "ведомого"): передача "1" от МК, передача "0" от МК, прием "1" от устройства и прием "0" от устройства.

Любой тайм-слот всегда начинает МК путем перевода шины 1-Wire в низкий логический уровень. Длительность любого тайм-слота должна находиться в пределах от 60 до 120 микросекунд. Между отдельными тайм-слотами всегда должен предусматриваться интервал не менее 1 микросекунды (конкретное значение определяется параметрами ведомого устройства).

Тайм-слоты передачи отличаются от тайм-слотов приема поведением МК: при передаче он только формирует сигналы, при приеме, кроме того, еще и опрашивает (т.е. принимает) уровень сигнала в линии 1-Wire. Следующй рисунок демонстрирует временные диаграммы тайм-слотов всех 4-х типов: вверху показаны тайм-слоты передачи от МК, внизу - приема от устройства.

Рисунок 6.26-Тайм слоты

Тайм-слот передачи "0" заключается просто в удержании шины 1-Wire в низком уровне в течение всей длительности тайм-слота. Передача "1" осуществляется путем "отпускания" шины 1-Wire со стороны МК не ранее чем через 1 микросекунду после начала тайм-слота, но не позже чем через 15 микросекунд. Ведомое устройство опрашивает уровень в шине 1-Wire в течение временного интервала, условно показанного в виде серого прямоугольника, т.е. начиная с 15-й микросекунды от начала тайм-слота и заканчивая 60-й микросекундой от начала. Типичный момент ввода уровня в устройство (т.е. характерный для большинства устройств) - около 30-й микросекунды от начала тайм-слота. Заштрихованная область - это область "нарастания" уровня в шине 1-Wire, которая зависит от емкости линии и сопротивления подтягивающего резистора, она приведена для справки. Тайм-слоты приема информации отличаются тем, что МК формирует только начало тайм-слота (абсолютно так же, как при передаче "1"), а затем управление уровнем шины 1-Wire берет на себя устройство, а МК осуществляет ввод этого уровня так же в определенной зоне временных интервалов. Зона эта, как видно из рисунка, довольно мала. Как и раньше, заштрихованная область - область неопределенности, поэтому для ввода, собственно говоря, контроллеру остается даже не промежуток, а скорее конкретный момент, когда он должен ввести уровень сигнала из линии. Этот момент времени - 14-я или 15-я микросекунда от начала тайм-слота. Разумеется, если линия имеет малую емкость, а подтягивающий резистор мал, зона опроса несколько расширяется.

Важно понимать, что следует очень тщательно подходить к обеспечению в шине 1-Wire требуемых временных интервалов, т.к., например, увеличение длительности тайм-слота вывода "0" свыше рекомендованного значения может привести к ошибочному восприятию этого тайм-слота, как сигнала RESET, и, разумеется, после этого вся процедура обмена пойдет насмарку.

Разобравшись с процедурами обмена битами, пора приступать к более высокому уровню протокола обмена информацией, и для этого необходимо рассмотреть принципы адресации устройств и управления ими.

Каждое устройство 1-Wire обладает уникальным идентификационным 64-битным номером, программируемым на этапе производства микросхемы. Уникальным - это значит, что фирма-производитель гарантирует, что не найдется двух микросхем с одинаковым идентификационным номером (по крайней мере в течении нескольких десятков лет при существующих темпах производства).

При рассмотрении протокола обмена мы будем исходить из принципа, что на шине 1-Wire имеется более одного устройства. В этом случае перед МК встают 2 проблемы: определение количества имеющихся устройств и выбор (адресация) одного конкретного из них для обмена данными. Решение первой проблемы осуществляется двумя путями: универсальным и простым.

Универсальный рассмотрим с командой поиск ПЗУ. А более простой заключается в том, что номера всех используемых в вашей схеме 1-Wire-устройств вы должны знать заранее, и просто использовать их как константы в вашей программе.

Номера некоторых устройств нанесены прямо на корпусе микросхем (например, для устройств iButton - всем известных ключей-таблеток), а номера других можно определить при помощи специальных программ или устройств.

Алгоритм передачи данных по шине 1-Wire следующий. После передачи импульса RESET микроконтроллер передает на шину команду. Данные команды называются команды ПЗУ.

| 1. READ ROM | 33H | Идентификация устройств |

| 2. SKIP ROM | CCH | Пропуск адресации |

| 3. MATCH ROM | 55H | Совпадение ПЗУ или адресация подчиненного устройства |

| 4. SEARCH ROM | F0H | Поиск ПЗУ, получение идентификационных данных о всех устройствах на шине |

| 5. OVERDRIVE ROM | 3CH | Ускоренная версия пропуска ПЗУ |

| 6. OVERDRIVE MATCH ROM | 69H | Ускоренная версия MATCH ROM |

Команда “Чтение ПЗУ” может использоваться на шине с одним подчиненным для чтения 64-разр. индивидуального ИК. Если имеется несколько подчиненных устройств, подключенных к шине, то результатом выполнения этой команды будет прием значения, эквивалентного логическому И между всеми ИК. При этом полагается, что связь безупречная, а наличие нескольких подчиненных индицируется ошибочным CRC.

Команда «Пропуск ПЗУ» может использоваться, если нет необходимости адресоваться к конкретному подчиненному устройству по его специфическому адресу. На шине с одним подчиненным команда “Пропуск ПЗУ” прекрасно подходит для его адресации. На шине с несколькими подчиненными команда “Пропуск ПЗУ” может использоваться для адресации всех устройств одновременно.

Это удобно, если требуется отправить общую команду нескольким подчиненным устройствам, например, одновременный запуск преобразования температуры в нескольких датчиках температуры. Команду “Пропуск ПЗУ” бессмысленно использовать при чтении шины с несколькими подчиненными устройствами.

Команда “Совпадение ПЗУ” используется для адресации конкретного подчиненного устройства на шине.

После выполнения команды “Совпадение ПЗУ” передается 64-разрядный ИК. По завершении, только тому подчиненному устройству, который принял свой ИК, разрешается отвечать после приема следующего импульса сброса.

Команда “Поиск ПЗУ” может использоваться, если идентификаторы подчиненных устройств неизвестны заранее. Это делает возможным обнаружить идентификаторы всех подчиненных устройств, подключенных к шине. Для этого, вначале передается команда “Пропуск ПЗУ”. Каждый подчиненный размещает первый бит своего идентификатора на шине. Ведущий считывает результат, как логическое И над всеми первыми битами идентификаторов всех подчиненных устройств. Затем подчиненные размещают на шине двоичное дополнение к первому биту своего идентификатора. Ведущий считывает состояние шины, которое есть результат логического «И» над всеми дополнениями к первому биту идентификатора всех подчиненных устройств. Если все устройства в первом разряде ИК содержат 1, то ведущий считает 10b. Аналогично, если значения 1 разряда всех устройств равно 0, то ведущий примет 01b. В этих случаях, бит может быть сохранен как значение первого бита всех адресов. После этого ведущий снова выполняет размещение этого бита на шине, чем сигнализирует подчиненным о необходимости дальнейшего продолжения передачи разрядов ИК. Если на шине будут присутствовать устройства, как с лог. 0, так и с лог. 1 в первом бите идентификатора, то ведущий примет 00. В этом случае, ведущий должен выбрать с какими адресами продолжать работу, с лог. 0 или 1 в первом разряде. Выбор передается по шине, указывая выбранным подчиненным о необходимости дальнейшей передачи ИК, а остальные подчиненные переходят в режим ожидания.

Затем ведущий переходит к считыванию следующих бит и этот процесс повторяется до считывания всех 64 бит. В результате ведущий обнаруживает полный 64-разрядный идентификатор. Для поиска других идентификаторов необходимо снова инициировать команду «Поиск ПЗУ», но в этом случае при возникновении несоответствий сделать другой выбор. Если придерживаться данной последовательности, то, в конечном счете, можно обнаружить все подчиненные устройства. Обратите внимание, что после выполнения первого поиска все подчиненные, кроме одного, переходят в режим ожидания. Таким образом, в этом состоянии связаться с активным подчиненным можно с помощью команды «Совпадение ПЗУ».

Последовательность связи по протоколу 1-Wire.

1. Ведущий отправляет импульс «сброс».

2. Подчиненные отвечают импульсом «RESENCE»

3. Ведущий отправляет команду ПЗУ, адресуя одно или несколько подчиненных устройств.

4. Ведущий отправляет команду памяти или команду функции.

Команды памяти/функций

Команды памяти/функций – команды, которые специфичны для конкретного типа ИС или их класса. Обычно эти команды относятся к чтению или записи внутренней памяти и регистров подчиненных ИС. Количество таких команд фиксировано, но все они поддерживаются конкретным видом подчиненного устройства. Последовательность чтения и записи определена для каждой ИС. В связи с этим команды памяти здесь в подробностях не рассматриваются.

JTAG

Www.jtag.ru

Под JTAG, подразумевается стандарт: IEEE 1149.1-2001 Test Access Port and Boundary-Scan Architecture (Стандарт IEEE 1149.1-2001 Порт тестового доступа и Архитектура Граничного сканирования).

С ростом степени интеграции БИС, плотности монтажа и появлением многослойных печатных плат, методы диагностики, основанные на подключении к контрольным точкам платы и выводам микросхем, становятся все более сложными в использовании и неэффективными.

Основные недостатки альтернативных способов диагностики были связаны, прежде всего, с отсутствием соответствующих общепринятых стандартов—и, как следствие, широкой поддержки проектировщиков и производителей.

В начале 1985 года объединенными усилиями нескольких европейских компаний была создана группа для разработки решения проблем тестирования интегральных схем, цифровых устройств и систем. Эта группа получила имя: Joint European Test Action Group (JETAG). Позднее, в 1988 году к ней присоединил

Дата добавления: 2021-09-07; просмотров: 591;