Последовательностная логика

Последовательностная логика (конечные автоматы с памятью) описывается в языке АНDL с помощью триггеров, регистров, машин состояний и библиотеки параметрических модулей (LMP).

Регистры. Регистр создается объявлением его в разделе VARIABLE или ссылкой в строке в разделе LOGIC. После определения регистра его можно подключить к другой логике при помощи его портов. Обращение к портам регистра производится по имени регистра и имени порта:

<имя регистра>.<имя порта>

В следующем примере сформирован восьмиразрядный регистр из триггеров D-типа, который защелкивает данные с входов d по положительному фронту синхросигнала при положительном активном значении на входе разрешения.

SUBDESIGN bur_reg

(

clk, load, d [7..0] :INPUT;

q [7..0] :OUTPUT;

)

VARIABLE

ff [7..0] :DFFE;

BEGIN

ff [ ] .clk = clk;

ff [ ] .ena = load;

ff [ ] .d = d [ ];

q [ ] =ff [ ] .q;

END;

Первое уравнение логической секции соединяет вход тактового сигнала проекта с тактовыми входами триггеров. Во втором уравнении подключается разрешающий сигнал, в третьем уравнении подключаются входы, а в четвертом выходы. Altera рекомендует использовать в качестве тактирующего глобальный синхросигнал.

Можно объявить выходы проекта как D-триггеры в разделе VARIABLE. Это дает экономию за счет использования триггеров на выводах микросхемы.

SUBDESIGN reg_out

(

clk, load, d [7..0] :INPUT;

q [7..0] :OUTPUT;

)

VARIABLE

q [7..0] :DFFE; % выходы объявлены как регистры %

BEGIN

q [ ] .clk = clk;

q [ ] .ena = load;

ff [ ] .d = d [ ];

q [ ] =d [ ];

END;

Счетчики. Счетчики обычно реализуются на D-триггерах с использованием оператора IF. В следующем примере реализован 16-разрядный загружаемый счетчик со сбросом.

SUBDESIGN ahdlcnt

(

clk, load, ena, clr, d[15..0] : INPUT;

q [15..0] :OUTPUT;

)

VARIABLE

count[15..0] : DFF;

BEGIN

count [ ] .clk = clk;

count [ ] .clm = !clr;

IF load THEN

count [ ] .d = count [ ] .q+1;

ELSE

count [ ] .d = count [ ] .q;

count Q .d = count)].q;

END IF;

q [ ] = count [ ];

END;

Реализация двунаправленных выводов

Порты программируемых микросхем в устройствах могут быть заданы как двунаправленные (BIDIR). Порты микросхемы (ножки микросхемы) так и обозначаются BIDIR, а подключение к ним осуществляется с помощью устройств, построенных на примитиве TRI (тристабильный вывод).

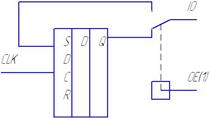

Рассмотрим триггер, который делает выборку значения, найденного на шине с тремя состояниями, а так же может передать обратно на шину хранимое значение.

SUBDESIGN BUS_REG

{ CLIK, OF: INPUT;

IO: BIDIR

}

BEGIN

IO = TRI (DFF (IO, CLK,,), OE)

END.

Двунаправленный сигнал IO запускается примитивом TRI, используется в качестве входа для D-триггера. Запятые в конце списка параметров определяют места для сигналов триггера SET и RESET. По умолчанию они установлены в неактивный уровень.

Дата добавления: 2021-09-07; просмотров: 581;