Прямой доступ к памяти

При работе в режиме прямого доступа к памяти (ПДП) контроллер ПДП выполняет следующие функции:

• принимает запрос на ПДП от внешнего устройства;

• формирует запрос микропроцессору на захват шин системной магистрали;

• принимает сигнал, подтверждающий вход микропроцессора в состояние захвата (перехода в z-состояние, при котором процессор отключается от системной магистрали);

• формирует сигнал, сообщающий внешнему устройству о начале выполнения циклов ПДП;

• выдает на шину адреса системной магистрали адрес ячейки ОП, предназначенной для обмена;

• вырабатывает сигналы, обеспечивающие управление обменом данными;

• по окончании ПДП либо организует повторение цикла ПДП, либо

прекращает режим ПДП, снимая запросы на него.

Циклы ПДП выполняются с последовательно расположенными ячейками памяти, поэтому контроллер ПДП имеет счетчик числа переданных байтов.

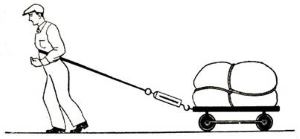

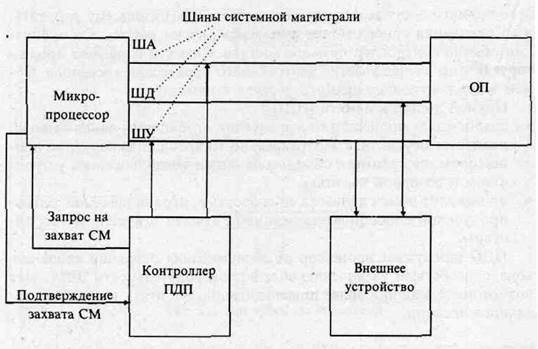

На рис. 6.4 приведена схема взаимодействия устройств микропроцессорной системы в режиме ПДП.

Контроллеры ПДП (КПДП) в IBM PC совместимы снизу вверх, т.е. программы, написанные с использованием КПДП ранних моделей ЭВМ, нормально работают и на более поздних моделях.

Рис. 6.4.Взаимодействие устройств в режиме ПДП

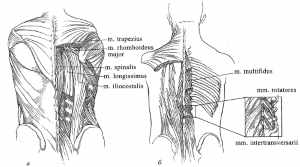

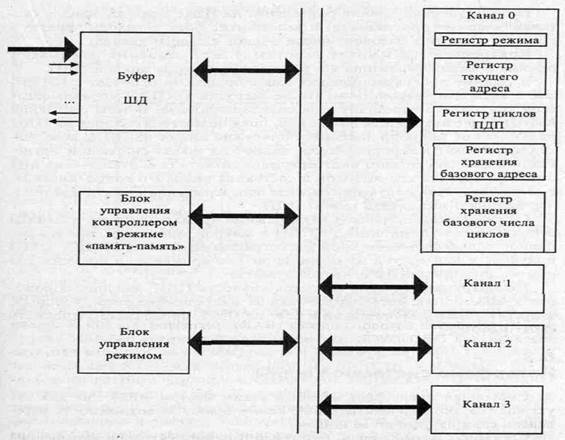

Каждый канал КПДП состоит из четырех 16-разрядных регистров (рис. 6.5): регистр текущего адреса (CAR), регистр циклов ПДП (CWR), регистр хранения базового адреса (BAR), регистр хранения базового числа циклов ПДП (WCR) и 6-разрядного регистра режима (MR).

Регистр текущего адреса хранит текущий адрес ячейки памяти при выполнении цикла ПДП. После выполнения каждого цикла ПДП содержимое этого регистра увеличивается или уменьшается на единицу. Оно может быть прочитано или загружено с помощью двух команд IN или OUT соответственно, каждая из которых работает только с одним байтом. В режиме автоинициализации содержимое регистра текущего адреса при обновлении принимает базовый адрес из регистра хранения базового адреса.

Регистр циклов ПДП хранит число слов, предназначенных для передачи. При выполнении циклов регистр работает в режиме вычитающего счетчика. При переходе из нулевого состояния в FFFFH вырабатывается управляющий сигнал для блока управления контроллером. Регистр может быть прочитан двумя командами IN. В него можно осуществить запись двумя командами OUT из микропроцессора или в режиме инициализации — из регистра хранения базового числа циклов ПДП.

Регистры BAR и WCR предназначены для хранения констант — базового адреса и базового числа циклов. Они загружаются в режиме программирования КПДП одновременно с регистрами CAR и CWR. В процессе выполнения циклов ПДП их содержимое не изменяется. Прочитать состояние этих регистров невозможно.

Регистр режима определяет режим работы канала. Он содержит информацию о номере канала, типе цикла ПДП (чтение (ОП ← ВУ), запись (ОП → ВУ), проверка), необходимости автоинициализации, режиме изменения регистра текущего адреса (CAR) — увеличение или уменьшение и режиме работы канала — передача по запросу, одиночная передача, блочная передача, каскадирование (работа в составе каскада КПДП).

Регистр команд блока управления режимом определяет основные параметры работы канала. Загружается при программировании КПДП микропроцессором. Регистр условий хранит разрешение на ПДП каждому каналу (устанавливаемые программно) и запоминает факт перехода через 0 в регистре хранения базового числа циклов каждого канала.

Контроллер ПДП может работать в двух основных режимах: в режиме программирования и в режиме выполнения циклов ПДП.

В режиме программирования микропроцессор работает с КПДП, как с внешним устройством. После загрузки в КПДП управляющих слов контроллер переходит в пассивное состояние. В этом состоянии КПДП будет находиться до тех пор, пока не поступит запрос на ПДП от ВУ или от микропроцессора. Обнаружив запрос на ПДП, контроллер выставляет микропроцессору запрос на захват системной магистрали и ожидает от него подтверждения захвата (т.е. отключения МП от СМ, перехода его выходов в состояние высокого сопротивления, г-состояния). При получении сигнала подтверждения захвата, контроллер начинает выполнять циклы ПДП.

Системная магистраль (СМ) в режиме прямого доступа к памяти используется мультиплексно КПДП и микропроцессором, причем основное управление системной магистралью выполняет КПДП, а МП получает к ней доступ на очень короткие промежутки времени для обмена информацией с основной памятью.

Рис. 6.5.Структурная схема контроллера ПДП

Несмотря на большую самостоятельность ПДП, ведущее положение в МП-системе остается все-таки за микропроцессором, который, запустив обмен информацией в режиме ПДП, продолжает выполнять свою работу.

Дата добавления: 2017-01-26; просмотров: 1460;