Обобщенный интерфейс микропроцессора

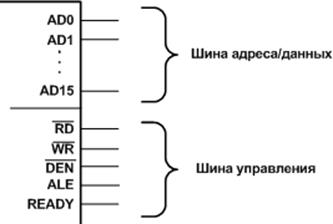

Обобщенный интерфейс микропроцессора включает шину данных, шину адреса и шину управления (рис.1).

|

Рис. 1.

Каждая шина состоит из нескольких проводников (линий связи), идущих параллельно.

Разрядность шины данных определяется разрядностью микропроцессора. Разрядность шины адреса определяется разрядностью адреса, используемого в данном микропроцессоре, и может отличаться от разрядности шины данных. Количество же линий в шине управления зависит от микропроцессора и способа организации в нем обмена с другими устройствами, входящими в состав МПС.

Обобщенный интерфейс микропроцессора представлен на рис. 2.

|

Рис. 2.

Он включает шину данных (в данном случае для примера — 16-ти разрядную), 16-разрядную шину адреса и шину управления, в которую входят сигналы, предназначенные для управления обменом в параллельном формате. Для реализации асинхронного обмена предусмотрен сигнал проверки готовности READY, с помощью которого ведомое устройство сообщает микропроцессору о своей готовности к обмену.

Часто с целью уменьшения количества выводов микропроцессора, для передачи адреса и данных используют одни и те же линии. При этом передача адреса и данных происходит в разные моменты времени (разделение во времени). Такой способ организации шины получил название мультиплексированная шина адреса-данных (рис. 3)

|

Рис. 3.

Сигнал ALE, входящий в состав шины управления, показывает, в какой момент времени по мультиплексированной шина передается адрес (рис. 4).

|

Рис. 4.

На рисунке представлена временная диаграмма цикла асинхронного обмена (на примере операции чтения из внешнего устройства). Как видно, обмен начинается с выставления адреса на шине адреса. Сигнал ALE показывает, что по мультиплексированной шине передается адрес. Затем устанавливается направление обмена с помощью сигнала RD, и сигнал начала обмена DEN переходит в активное состояние. Далее происходит анализ готовности ведомого устройства. Если устройство не готово (сигнал READY=0), микропроцессор переходит в состояние ожидания. После активизации сигнала готовности происходит собственно ввод данных, предоставленных по шине данных ведомым устройством.

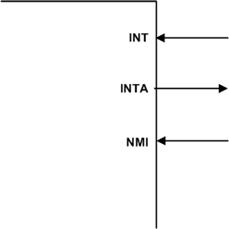

Для организации обмена по прерываниям в интерфейсе микропроцессора должны быть предусмотрены специальные управляющие сигналы (они входят в состав шины управления), (см. рис. 5).

|

Рис. 5.

Сигнал INT — запрос на прерывание от внешнего устройства. Сигнал INTA— подтверждение прерывания (микропроцессор этим сигналом сообщает внешнему устройству, что он готов обработать запрос). Сигнал NMI — запрос немаскируемого прерывания, аналогичен сигналу INT. Немаскируемое прерывание обрабатывается микропроцессором всегда, в то время как обработка обычных прерываний (по входу INT) может быть запрещена (с помощью специальной команды) на время выполнения критических участков программы. Ко входу запроса немаскируемого прерывания обычно подключаются сигналы, информирующие МП о событиях, имеющих жизненно важное значение для работы МПС (например, сигнал о понижении напряжения питания — микропроцессор должен принять немедленные меры для сохранения данных).

Временная диаграмма изменения сигналов запроса/подтверждения прерывания приведена на рис.6.

|

Рис. 6.

Временной разрыв между активизацией сигналов INTи INTAвызван необходимостью завершения текущей команды микропроцессором.

В дополнении к указанным сигналам, на микропроцессор обязательно подаются тактовые импульсы от тактового генератора, которые позволяют синхронизировать работу всех узлов процессора (рис. 7).

|

Рис. 7.

Для подачи импульсов служит вход CLK микропроцессора.

Дата добавления: 2019-02-08; просмотров: 794;