Статичні запам'ятовувачі ВІС ОЗП

Це двостанові комірки пам'яті - тригери, які крім зберігання одиниці біт інформації (1 або 0), дозволяють здійснювати операцію звертання WR/RD. Вони є найбільш поширеними у практиці цифрової та мікропроцесорної техніки і застосовуються як регістри процесорів надоперативної та буферної пам'яті.

За технологічним виконанням статичні запам'ятовувачі розрізняють на біполярні та польові. Біполярні запам'ятовувачі, хоч і мають серед статичних ОЗП найвищу швидкодію (tВ=5...50нс), однак порівняно з польовими (на ПТ) мають значно меншу інформаційну місткість і досить значну потужність споживання. Це пояснюється тим, що польові запам'ятовувачі займають на кристалі у кілька разів меншу площу, ніж біполярні, та й споживають менший струм.

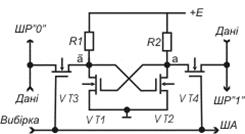

На рис. 6.1 зображено схему статичного польового запам'ятовувача на базі n-МОН-структури. Транзистори VТ1 і VТ2 утворюють тригер, а транзистори VТЗ і VТ4 - двонапрямлені ключі вводу/виводу даних, тобто звертання WR/RD. Резистори навантаження R1 і R2 мають високі номінали опорів для забезпечення низького споживання у режимі зберігання.

Схема польового запам'ятовувача має три інформаційні виводи, від логічних станів (0 або 1) на яких залежить той чи інший режим роботи. Зокрема, це два виводи (станів  і

і  тригера) шин розрядів (ШР) "1" і ШР "0" і вивід вибірки схеми - шини адреси (ША).

тригера) шин розрядів (ШР) "1" і ШР "0" і вивід вибірки схеми - шини адреси (ША).

Рис. 5.62 Статична однобітова комірка пам’яті на польових транзисторах

У режимі запам'ятовування транзистори VТ3 і VТ4 закриті, а у режимі звертання WR/RD - відкриті. Режим запам'ятовування визначає низький потенціал на АШ, а звертання - високий. В останньому випадку, коли транзистори VТЗ і VТ4 відкриті і стають провідними в обох напрямках, можна виконувати як запис, так і зчитування інформації.

У режимі запису на ШР "1" і ШР "0" встановлюються високий або низький рівні сигналів, які відкривають транзистор VТ1 або VТ2, і тригер переходить в стан лог. 0 або лог. 1. При зчитуванні інформації із запам'ятовувача на ШР "1" і ШР "0" подається високий потенціал джерела живлення. У результаті цього розряджається паразитна ємність шини (ШР "1" або ШР "0"), яка зв'язана з відкритим транзистором (VT1 або VТ2) тригера. У відкритому транзисторі потенціал на виході близький до нуля (наприклад, якщо VТ1 відкритий, то  =0, а Q=1, бо VТ2 – закритий). Отже, при відповідній різниці потенціалів на розрядних шинах (ШР "1"=0, а ШР "0"=1 чи навпаки) дана інформація із запам'ятовувача буде зчитуватися на вихідні буферні підсилювачі шин.

=0, а Q=1, бо VТ2 – закритий). Отже, при відповідній різниці потенціалів на розрядних шинах (ШР "1"=0, а ШР "0"=1 чи навпаки) дана інформація із запам'ятовувача буде зчитуватися на вихідні буферні підсилювачі шин.

Порівняно з іншими статичні запам'ятовувачі на КМОН-транзисторах споживають найменше потужності. Наприклад, потужність розсіювання у КМОН ВІС ОЗП КР537РУ2А, місткість якого 4К, складає всього 0,5мВт у режимі зберігання і 20мВт у режимі перемикання (звертання). Статичні ВІС ОЗП середньої швидкодії, що виконані на n-МОН-, КМОН- та І2Л-технологіях, мають період циклу звертання до запам'ятовувачів від сотень наносекунд до одиниць мікроcекунд. Перспективними ВІС ОЗП є, однак, ЗП на базі арсеніду галію. Потужність розсіювання у режимі звертання у таких ВІС складає не більше 10мкВт/біт, а час вибірки не перевищує 10нс.

У структурі ВІС ОЗП статичні запам'ятовувачі компонуються у прямокутну матрицю розміром п´m ( де n - число m-розрядних слів), яку називають накопичувачем ЗП. Кожний рядок накопичувача – це адресна шина вибірки, а стовпець – дві розрядні шини звертання ШР "1" і ШР "0" запам'ятовувача.

Дата добавления: 2016-07-22; просмотров: 2031;