Одноразрядный двоичный сумматор

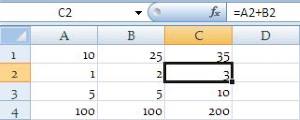

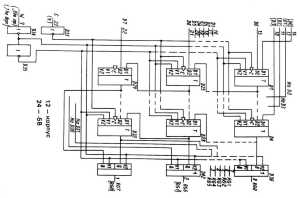

Одноразрядный двоичный сумматор является комбинационной схемой с тремя входами и двумя выходами (рис.3.18).

При параллельном суммировании на входы каждого разряда сумматора поступают значения цифр а и b соответствующих разрядов слагаемых и значение переноса p с младших разрядов сумматора. На выходе одноразрядного сумматора формируются значения цифры соответствующего разряда суммы Sи переноса в старший разряд сумматора P.

Значения S и P таблицы истинности одноразрядного сумматора построена на основе сложения и умножения для двоичной системы счисления.

| Таблица истинности выходов одноразрядного сумматора | |||||

| № | Входы | Выходы | |||

| a | b | p | S | P | |

Для каждого выходного сигнала составляются все комбинации входных сигналов, при которых выходные сигналы S и P принимают единичные значения:

,

,

.

.

Эти уравнения являются совершенной дизъюнктивной нормальной формой логических функций (СДНФ). В этой форме логическая функция (ЛФ) представляется в виде дизъюнкций конституэнт единицы.

Конституэнта единицы – это конъюнкция всех значений входных переменных: в прямой форме для единичных значений переменных, или в инверсной форме для нулевых значений переменных.

СДНФ позволяет записывать любые переключательные функции от двух переменных, используя только три основных логических операции И, ИЛИ, НЕ.

Следующим этапом проектирования является минимизация логических функций (не всегда возможна).

Из таблицы истинности видно, что переменная P принимает значение только для таких комбинаций входных переменных, когда хотя бы две переменные имеют единичные значения. Это можно записать в виде:

.

.

Анализируя функцию S можно заметить, что значение S равно единице, если в комбинациях входных сигналов присутствует хотя бы один единичный сигнал, и нет одновременно двух единичных значений переменных (компонента:  =

=  ) или есть совпадение трех входных единичных сигналов (компонента abp), т.е.:

) или есть совпадение трех входных единичных сигналов (компонента abp), т.е.:

Построение функциональной схемы по ПФ:

.

.

Для реализации ПФ для выхода Р требуется :

· три конъюнктора (схемы И) на два входа,

· дизъюнктор (схема ИЛИ) на 3 входа.

Для реализации ПФ для выхода S требуются:

· дизъюнктор (схема ИЛИ) на 3 входа,

· инвертор (схема НЕ),

· конъюнкторы (схемы И) на 2 и 3 входа.

· дизъюнктор (схема ИЛИ) на 2 входа.

Функциональная схема одноразрядного сумматора представлена на рис.3.19.

В этой схеме использована совместная минимизация уравнений, при которой для формирования разных выходных значений (S и P) используются общие логические схемы. Совместная минимизация позволяет получать схемы с минимальным количеством используемых элементарных вентилей, которое определяется по общему количеству входов. Такие схемы, как правило, имеют большую задержку выходных сигналов, которая определяется по максимальному количеству элементов пути его формирования.

По этой причине часто одноразрядный сумматор строят без совместной минимизации схем формирования выходных сигналов по уравнениям:

,

,

.

.

Дата добавления: 2020-10-25; просмотров: 439;