ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

Логическими элементами (ЛЭ) называются функциональные устройства, с помощью которых реализуются элементарные логические функции (рис.32). Они обычно используются для построения сложных преобразователей цифровых сигналов комбинационного типа, в которых отсутствует внутренняя память. Сигналы на их выходах в любой момент однозначно определяются сочетаниями сигналов на входах и не зависят от предыдущих состояний схемы.

| Рис. 32. Обозначение простейших логических элементов

|

ЛЭ выполняются в виде ИМС, в которых чаще всего используется, так называемая положительная логика: логическая 1 соответствует высокому, а логический 0 – низкому уровням напряжения. Если наоборот, то логика отрицательная.

В зависимости от компонентов логического элемента и способа их соединения различают следующие типы логик: диодно-транзисторная логика (ДТЛ) ;

транзисторно-транзисторная логика (ТТЛ).

ТРИГГЕРЫ

Триггер – логическое устройство, имеющее два устойчивых состояния, переход которого из одного состояния в другое осуществляется под воздействием управляющих сигналов.

Устойчивые состояния можно принять в качестве логической информации 0 и 1. В таком случае триггер можно использовать в качестве запоминающего устройства, которое хранит один разряд числа, представленного в двоичном коде.

В триггерах с прямым управлением активным уровнем считается уровень логической 1, а в триггерах с инверсным управлением– уровень логического 0. После переключения триггера входной активный уровень может быть снят, но триггер продолжает оставаться в том состоянии, которое он приобрел под воздействием этого сигнала. Для удобства-использования триггеры имеют два выхода, один из которых называют прямым Q, а другой – инверсным  . Если триггер установлен (в состоянии 1), на его прямом выходе будет логическая 1, а на инверсном – логический 0.

. Если триггер установлен (в состоянии 1), на его прямом выходе будет логическая 1, а на инверсном – логический 0.

Помимо информационных входов, обозначаемых буквами R,S,.J, К', D. Т,

триггеры могут содержать и вспомогательные (управляющие) входы, напримеp, предварительной установки или вход синхронизации С.

Триггеры, которые реагируют на информационные сигналы только при наличии сигнала синхронизации, называют синхронными. В отличие от них асинхронные триггеры реагируют на информационные сигналы в момент их поступления. Синхронные триггеры, в свою очередь, могут быть со статическим и динамическим управлением.

| а)б)в)

Рис.33. Обозначение синхронного триггера: а – с динамическим прямым

С-входом; б – с динамическим

инверсным С-входом;

в – со статическим управлением

|

Для того чтобы синхронный триггер со статическим управлением смог воспринимать сигналы на информационных входах, на его входе синхронизации С должен присутствовать уровень логической 1. Синхронный триггер со динамическим управлением реагирует на информационные сигналы только в момент изменения сигнала на С-входе от 0 до 1 (прямой динамический С-вход), либо от 1 до 0 (инверсный динамический С-вход). На рис. 33,а,б показаны соответственно обозначения синхронного триггера с прямым и инверсным динамическим управлением.

Для синхронного триггера со статическим управлением иногда используют обозначение С-входа, показанное на рис.33,в, но чаще всего у С-входа вообще не ставят никаких специальных значков.

По функциональным возможностям различают:

– триггер с раздельной установкой состояний 0 и 1 (триггер с установочными входами, RS-триггер);

– триггер со счетным входом (счетный триггер, T-триггер);

– триггер задержки с приемом информации по одному входу (D-триггер);

– универсальный триггер с информационными входами К и J (JK-триггер).

Асинхронный RS-триггерс раздельной установкойсостояний 1 и 0 имеет всего лишь два информационных входа: S (вход установки) и R (вход сброса). При активном уровне сигнала на входе установки S и пассивном уровне на входе R триггер, независимо от предыдущего состояния, принимает на выходе Q состояние 1. С другой стороны, при активном уровне сигнала на входе сброса R и пассивном уровне на входе S независимо от предыдущего состояния триггер переводится в состояние Q=0 (сбрасывается). При пассивном уровне сигнала на обоих входах состояние триггера не изменяется (режим хранения предыдущего состояния). Наконец, последняя из возможных комбинаций, когда на обоих входах одновременно присутствуют активные уровни, для триггеров этого типа просто запрещается, так как по описанному закону работы его выходное состояние будет непредсказуемым.

Сформулированный словесно закон функционирования асинхронного RS-триггера представлен в виде таблицы переходов триггера (рис. 34,а), где обозначено Qt– выходное состояние триггера до момента подачи соответствующей комбинации уровней (Rt St) на его информационные входы, Qt+1– состояние триггера после этого момента, А – активный, П – пассивный уровень. RS-триггер можно построить из логических элементов И – НЕ или двух ИЛИ – НЕ

(рис. 34).

Если на вход R элемента D1 (рис. 34, б) подана 1, то на выходе этого элемента ИЛИ – НЕ будет 0, а на выходе другого элемента D2 будет 1, поскольку выход D1соединен с одним из входов D2. При подаче на вход S элемента D2 сигнала высокого уровня (1), на его выходе будет 0, а на входе элемента D1 будет 1, поскольку выход D2 соединен с одним из входов D1. Рассуждая аналогично

| Рис. 34. RS-триггер: а – таблица переходов асинхронного RS-триггера,

б – с прямым управлением на элементах ИЛИ – НЕ,

в – с инверсным управлением на элементах И –НЕ

|

| №

| Rt

| St

| Qt

| Qt+1

| Режим

| |

| П

| П

| Q1

| Q1

| Хранение

| |

| П

| А

| Q1

|

| Установка в 1

| |

| А

| П

| Q1

|

| Сброс в 0

| |

| А

| А

| Q1

| Не определено

| Запрещенная комбинация

на входах

|

|

получим схему асинхронного RS-триггера, с инверсным управлением на элементах И – НЕ (рис. 34, в)

Триггером задержки (D-триггером) называют синхронный триггер (рис. 35, а), выходное состояние которого совпадает с сигналом на его единственном информационном входе (D-входе), которое тот имел на предыдущем такте импульсов синхронизации.

Сигнал на выходе Q начинает повторять сигнал на D-входе во время действия синхронизирующего импульса. Это значение хранится в триггере до прихода следующего синхронизирующего импульса. Примером D-триггера может служить микросхема К155ТМ2 – два D-триггера с асинхронными входами (рис. 35, а). На рис. 35, б приведены временные диаграммы, иллюстрирующие прохождение входного сигнала D на выход Q при при различных сигналах синхронизации C.

| Рис. 35. D-триггер: а – обозначение микросхемы К155ТМ2;

б – временные диаграммы, поясняющие его работу

|

JK-триггеры являются наиболее универсальными. Имеют два информационных входа: J и K. Функционирует подобно RS-триггеру с разницей, что не имеет запрещенной комбинации входных сигналов. На рис. 37, а дана таблица переходов, из которой видно, что при подаче на оба входа сигнала 1, на выходе триггера изменяется состояние на противоположное.

На основе JK-триггеров реализуются RS-, D- и Т-триггеры. Если использовать входы J и K, как входы S и R и исключить запрещённую комбинацию, когда на оба входа подан сигнал 1, то получим RS-триггер. Если вход К соединить с входом J инвертором, то получим D-триггер (рис.37, в). Если на оба входа: J и K – подать сигнал высокого уровня (установить 1) и использовать вход C для поступления сигналов, то получим T-триггер.

Т-триггер (рис. 37,в,) изменяет свое состояние на противоположное при поступлении на вход Т запускающего импульса. Т-триггеры называют триггерами со счетным входом. В интегральном исполнении Т-триггеры не выпускаются, так как они легко получаются из RS-, JK- или D-триггеров (рис. 37,д).

| Рис. 37. Таблица переходов (а), условное обозначение универсального JK-триггера (б) и Т-триггера (в), реализация

D-триггера (г) и Т-триггера (д) на основе JK-триггера

|

| №

| Kt

| Jt

| Qt

| Qt+1

| Режим

| |

| П

| П

| Qt

| Qt

| Хранение

| |

| П

| А

| Qt

|

| Установка в1

| |

| А

| П

| Qt

|

| Сброс в 0

| |

|

А

|

А

|

Qt

| _

Qt

|

Счет

|

|

Контрольные вопросы:

1. Что называют логическим элементом?

2. Какими устойчивыми состояниями обладает логический элемент?

3. Изобразите временную диаграмму логического элемента ИЛИ.

4. Что такое триггер?

5. В чем разница между синхронным и асинхронным триггерами?

Литература: [3] с. 107-112, 118-122.

Лекция 25.КОМБИНАЦИОННЫЕ УСТРОЙСТВА

план: дешифратор, мультиплексор, сумматор, счетчики импульсов.

Дешифратор (преобразователь кода) – это устройство для преобразования кода числа на входе (комбинации входных сигналов) в сигнал на определенном выходе. Дешифраторы преобразуют: двоичный код, двоично-десятичный код, код Грея.

Если при n входах дешифратор имеет m = 2n выходов, то такой дешифратор называется полным, при m < 2n – неполным или частичным.

Двоично-десятичныйдешифратор преобразует двоичный код в семисегментный (неполный). Он используется при выводе числа на знаковый семисегментный индикатор (например, в часах).

Мультиплексор – логическое устройство для последовательного опроса нескольких двоичных переменных и передачи их на один выход. Простейший мультиплексор можно представить в виде ключа, управляемого сигналом А. В зависимости от этого сигнала на выход пройдет или сигнал х0, или х1.

Мультиплексор на четыре входа (рис.39) должен иметь два управляющих сигнала А0 и А1 (на восемь входов – три управляющих сигнала А0, А1 и А2).

Таким образом, количество адресных входов (управляющих сигналов) должно быть таким, что бы в двоичном коде адресовать все входы.

| Рис. 39. Мультиплексор: а – схема работы; б – таблица соответствия сигналов; в – условное графическое обозначение

|

Сумматор – устройство, выполняющее операцию сложения цифровых кодов двух чисел.

Простейший сумматор двух двоичных переменных А и В (рис.40) имеет два входа для двоичных чисел А и В, выход для суммы S (результат сложения в разряде, вес которого равен весу операнда) и выход С для переноса в следующий сумматор (С равен 1, если веса S не хватает для отражения результата).

Для построения многоразрядных сумматоров необходимо учитывать многоразрядный перенос из младшего разряда в старший.

| Рис. 40. Сумматор двух двоичных переменных:

а – схема сумматора; б – таблица истинности

|

Сумматор двухразрядных чисел (рис.41) имеет четыре входа (по два на каждое число), два выхода для записи суммы в виде двухразрядного числа (S0 и S1) и выходы для учета переноса (при С0 = 1 к результату добавляется единица для учета переноса от сложения более младших разрядов).

| Рис. 41. Сумматор двухразрядных чисел: а – обозначение; б – таблица истинности

|

Применяются последовательные и параллельные многоразрядные сумматоры. У сумматора с параллельным переносом время выполнения операции суммирования значительно меньше, чем у последовательного сумматора. Для чисел большой разрядности применяют сумматоры с групповым переносом.

СЧЕТЧИКИ ИМВУЛЬСОВ

Счетчиком импульсов называют устройство, предназначенное для подсчета числа импульсов, поступающих на его вход, и хранения результата счета в виде кода. Выходная информация может быть в двоичном или двоично-десятичном коде. Счетчики широко применяются в измерительной технике и устройствах цифровой обработки информации. Практически любую аналоговую величину (перемещение, скорость, длительность процесса и т.д.) можно преобразовать в электрические импульсы, число которых пропорционально значению аналоговой величины, подсчитать эти импульсы с помощью счетчика и выразить числом или кодом. Счетчики выполнены на основе триггеров, образующих двоичные разряды. Количество разрядов определяется наибольшим числом, которое должен зафиксировать счетчик. В n-разрядном счетчике имеется один вход для счета импульсов и n-выходов для выдачи кода числа подсчитанных импульсов.

По целевому назначению счетчики подразделяются на простые и реверсивные. Простые могут быть суммирующими и вычитающими (импульс +1 или – 1). Реверсивные счетчики могут переключаться из суммирующего в вычитающий и наоборот. По способу организации цепей переноса счетчики бывают с последовательным и параллельным переносом.

Рассмотрим схему трехразрядного асинхронного двоичного счетчика (рис. 42,а).

В некоторый момент счётчик устанавливается в нулевое состояние с помощью импульса на входе R. После поступления импульса на входе C через некоторое время t3.1на выходе первого Т-триггера появляется 1. После поступления второго импульса на вход C на выходе первого Т-триггера устанавливается 0, а на выходе второго Т-триггера – 1. После поступления третьего импульса на выходе первого триггера устанавливается 1, на выходе второго триггера –1 и т.д. При этом состояние на выходах триггера Q0, Q1, Q2 в двоичном коде соответствуют номеру поступившего сигнала.

Для увеличения количества разрядов счетчиков применяют их каскадное соединение друг за другом, для чего в схеме счетчика предусматривается специальный выход Р, с которого снимают сигнал переноса на информационный вход следующего счетчика. Для этой цели в схеме счетчика введен дополнительный логический элемент 4И, на входы которого поступают сигналы с входа С и с выходов Q0, Q1, Q2. При появлении восьмого импульса на выходе Р появляется сигнал 1, который используют в качестве сигнала переноса на вход следующего счетчика. Прохождение сигналов сопровождается задержками (tз.1, tз.2 и т.д.), и по этой причине при большом числе разрядов счетчика задержка может быть значительной, что и ограничивает его быстродействие.

| Рис. 42. Трехразрядный суммирующий счетчик: а – схема счетчика; б – временные диаграммы, поясняющие работу; в – таблица состояний

|

В настоящее время выпускается обширная номенклатура счетчиков от простейших до многоразрядных двоичных и десятичных. Существуют также микросхемы, объединяющие десятичный счетчик с дешифратором для управления семисегментным цифровым индикатором.

Рассмотренный счетчик является суммирующим асинхронным счетчиком с последовательным переносом. Чтобы получить вычитающий счетчик, нужно в предыдущей схеме вход каждого последующего триггера соединить с инвертирующим входом предыдущего. Если на входах каждого разряда включить схему управления, то можно получить реверсивный счетчик.

Контрольные вопросы:

1. Что такое дешифратор?

2. Что такое мультиплексор?

3. Что такое счетчик импульсов?

4. Как можно увеличить количество разрядов счетчика?

Литература: [3] с. 113-116, 123-125.

Лекция 26. КОМБИНАЦИОННЫЕ УСТРОЙСТВА

план: регистры, микропроцессоры.

РЕГИСТРЫ

Регистры – устройства, предназначенные для приема хранения и передачи информации, представленной двоичным кодом. Каждому разряду двоичного кода соответствует определенный разряд регистра. С помощью регистров можно выполнять некоторые логические операции, а также преобразовывать информацию одного вида в другой (например, из последовательного кода в параллельный).

Регистр представляет собой совокупность определенным образом соединенных триггерных ячеек с устройством управления входными и выходными сигналами.

По способу ввода и вывода (приема и передачи) регистры подразделяются на параллельные, последовательные и последовательно-параллельные. Регистры с параллельным приемом и выдачей информации (регистры памяти) выполняют на основе синхронных D-триггеров. На рис. 43 дана упрощенная схема двух разрядов многоразрядного регистра памяти.

| Рис. 43. Регистры памяти:

а – упрощенная схема;

б – диаграммы состояний;

в – графическое обозначение

регистра К580ИР82

|

Поступающая информация в виде совокупности сигналов на входах (D0, D1 и т.д.) после выдачи сигнала записи  сохраняется на входах триггеров и может храниться там неопределенно долгое время после снятия сигналов D0, D1. Для чтения записанной информации подается сигнал

сохраняется на входах триггеров и может храниться там неопределенно долгое время после снятия сигналов D0, D1. Для чтения записанной информации подается сигнал  на входы шинных формирователей.

на входы шинных формирователей.

Последовательные регистры (сдвиговые регистры) состоят из последовательного соединения триггеров. Под действием тактовых импульсов состояние каждого триггера передается следующему, что равносильно сдвигу кода. Ввод данных производится синхронно под действием тактовых импульсов С.

Сдвиговые регистры позволяют осуществлять логическую операцию сдвига кода записанного числа на любое количество разрядов. Сдвиг применяется для преобразования параллельного кода в последовательный и наоборот, для операций умножения и деления (сдвиг влево на один разряд – это умножение на два, вправо – деление на два).

На рис. 44 представлена упрощенная схема сдвигового регистра. Поданный на вход D первого триггера сигнал DR после поступления первого импульса на продвигающей шине С будет сохранен в первом D-триггере и при необходимости его можно прочесть в виде сигнала Q0. При поступлении второго импульса на продвигающей шине С сигнал DR будет передвинут во второй триггер и появится на входе Q1, затем после третьего импульса С – на выходе Q и т.д. (рис. 3.18,б).

| Рис. 44. Сдвиговый регистр: а – схема;

б – диаграммы состояний

|

МИКРОПРОЦЕССОР

Основным узлом всех устройств микропроцессорной техники является микропроцессор (МП) или однокристальный микроконтроллер (ОМК). В МП процесс обработки информации осуществляется программно, т.е. путем последовательного выполнения элементарных действий – команд программы, и результат обработки определяется этой программой. Решаемая задача, таким образом, задается программой, а сами аппаратные средства (микропроцессор и набор дополнительных ИС) остаются неизменными. Это определяет универсальность устройств и систем на основе МП.

Микропроцессором называется программно-управляемое устройство в виде интегральной микросхемы, обрабатывающее цифровую информацию и управляющее этим процессом. МП может принимать, дешифрировать и выполнять команды, представленные в двоичном коде.

Однокристальные микроконтроллеры (ОМК) являются наиболее массовыми представителями микропроцессорной техники. Интегрируя на одном кристалле высокопроизводительный процессор, память и набор периферийных устройств, они позволяют с минимальными затратами реализовать широкую номенклатуру систем управления различными объектами и процессами.

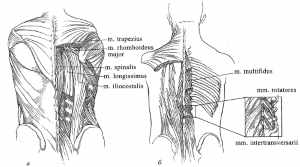

Основными внутренними компонентами МП являются арифметико-логическое устройство, реализующее множество арифметических и логических функций МП, узел синхронизации и управления, воспринимающий и генерирующий внешние управляющие сигналы; набор регистров для временного хранения кодов команд, данных, адресов и информации о внутреннем состоянии МП (рис.45).

Содержимое некоторых из внутренних регистров МП может быть изменено программным путем, другая их часть недоступна программисту. Общее число внутренних регистров МП разных семейств различно, как различны конкретные функции, выполняемые ими. Тем не менее при всем многообразии внутренних регистров МП наиболее значимыми являются следующие виды.

Рис.45. Внутренняя организация микропроцессора

Регистр команды воспринимает код текущей команды с шины данных и хранит его в течение всего времени ее исполнении. Регистр команды недоступен программисту.

Для хранения данных и промежуточных результатов в МП используются программно-доступные рабочие регистры. Если все рабочие регистры в составе МП позволяют непосредственно записывать в них результаты вычислений, выполненных АЛУ, их обычно называют регистрами общего назначения (РОН). Если в МП имеется всего лишь один такой специализированный регистр, его называют аккумулятором.

Программный счетчик (РС) обеспечивает хранение двоичного кода адреса ячейки памяти, где помещена команда, которую предстоит выполнить процессору вслед за исполняемой им в данный момент командой.

Новый цикл выбора команды МП всегда начинается с того, что на его шине адреса появляется содержимое РС, и очередная команда по этому адресу переписывается с шины данных в регистр команд, после чего она поступает на дешифратор команды. Выходы дешифратора подключены к узлу синхронизации и управления, определяющему требуемое для выполнения этой команды направление передачи данных и реагирующему на внешние сигналы, поступающие по шине управления от других устройств. В процессе исполнения команды содержимое РС автоматически увеличивается. Таким образом, в любой момент времени его содержимое представляет собой адрес очередной ячейки памяти, где может храниться либо следующая команда, либо дополнительные данные, привлекаемые МП для исполнения данной команды.

Регистр-указатель стека SP используется для хранения адреса последней использованной ячейки стека (области памяти, размер которой изменяется в процессе обработки). Работа стека организована по принципу «последним пришел – первым вышел». При записи данных в стек содержимое регистра SP автоматически уменьшается, и по этому адресу данные заносятся в память. При удалении данных из стека они переписываются из ячейки, адрес которой хранится в SP, после чего его содержимое автоматически увеличивается. Таким образом, этот регистр всегда следит за положением вершины стека (наиболее удаленной от начала стека ячейки памяти).

Информация об особенностях результата последней операции, выполненной АЛУ (информация о внутреннем состоянии МП), хранится в регистре флажков (другие его названия – регистр состояния, регистр кода условия).

Рассмотренные основные компоненты в составе МП связаны между собой быстродействующей внутренней шиной данных, а его внешние шины отделены от нее буферными каскадами, повышающими нагрузочную способность внешних шин. Отметим, что разрядность МП определяется числом бит данных, обрабатываемых в одной операции АЛУ, и всегда равна числу проводников внешней шины данных. Объем адресуемой памяти МП зависит от проводников внешней адресной шины. Что позволяет МП осуществлять операции ввода/вывода подобно обращению к обычной ячейке памяти.

Все операции в МП инициируются импульсами синхронизации от внешнего (реже встроенного) генератора тактовых импульсов (ТГ), стабилизированного кварцевым резонатором. По значению частоты следования импульсов синхронизации в первом приближени

Дата добавления: 2016-05-27; просмотров: 1015;

. Если триггер установлен (в состоянии 1), на его прямом выходе будет логическая 1, а на инверсном – логический 0.

. Если триггер установлен (в состоянии 1), на его прямом выходе будет логическая 1, а на инверсном – логический 0.

сохраняется на входах триггеров и может храниться там неопределенно долгое время после снятия сигналов D0, D1. Для чтения записанной информации подается сигнал

сохраняется на входах триггеров и может храниться там неопределенно долгое время после снятия сигналов D0, D1. Для чтения записанной информации подается сигнал  на входы шинных формирователей.

на входы шинных формирователей.