С х е м а «ИЛИ – НЕ».

Элемент ИЛИ – НЕ называют также: стрелка Пирса (Pierce arrow), NOR (сокращенное от NOT OR).

Алгебраическая запись функции ИЛИ – НЕ:

Аналог для логического элемента «ИЛИ - НЕ» на рис.8.18 представляет собойпоследовательно соединенные источник питания, контакты К1.1, К2.1 и лампунакаливания HL1. Переключатели SB1 и SB2 имитируют электрические сигналы навходе аналога, а нить лампы индицирует уровень сигнала на выходе. Разомкнутоесостояние контактов переключателей соответствует напряжению низкого уровня(логический нуль), замкнутое - высокому уровню (логическая единица).

Рисунок 8.18 - Логический элемент «ИЛИ – НЕ»

Таблица истинности состояния показывает, что на выходе элемента может быть единица только при одном условии, если на обоих входах будут логические нули.

Таблица истинности состояния показывает, что на выходе элемента может быть единица только при одном условии, если на обоих входах будут логические нули.

|

В отличие от рассмотренных ранее схем в ней вместо нагрузочного резистора RK имеется МОП-транзистор (на схеме рис. 8.19 он обозначен ТK). Это связано с тем, что нагрузочный резистор сильно увеличил бы площадь схемы. Логические транзисторы Т1 и Т2 включены параллельно. Входное напряжение на каждом из них равно напряжению затвора: UВХ1 = UЗИ1, UВХ2 = UЗИ2; выходное напряжение равно напряжению стока: UВЫХ = UСИ. Напряжение питания обычно выбирают в три раза большим порогового Uпор (Uпор - напряжение на затворе, при котором образуется канал).

Если Uпор = 2,0В, то логический перепад (разность между входным и пороговым напряжениями) составляет 4В. Логические уровни соответствуют выходным напряжениям открытого и закрытого транзисторов. Если на оба входа подать напряжение меньше порогового (соответствующее логическому нулю), то транзисторы T1 и Т2 окажутся закрытыми, а ток стока - практически равным нулю. При этом ток стока нагрузочного транзистора ТK тоже будет равен нулю. Поэтому на выходе установится напряжение, близкое к напряжению источника питания ЕC и соответствующее логической «1».

Если на вход хотя бы одного транзистора подать напряжение, превышающее пороговое (соответствующее логической «1»), то этот транзистор откроется и появится ток стока. Тогда на выходе схемы будет остаточное напряжение, значительно меньшее порогового, что соответствует логическому «0».

Следует отметить, что схемы на МОП-транзисторах менее быстродействующие, чем на биполярных. Это связано со скоростью перезарядки выходной емкости, которая весьма значительна. Все способы повышения быстродействия ведут к появлению других существенных недостатков.

Аналогично работает (с учетом полярностей) схема «ИЛИ – НЕ» с р-канальными МОП-транзисторами. Тип схемы влияет на характеристики (потребляемая мощность, быстродействие и др.), но принцип работы схемы остается неизменным.

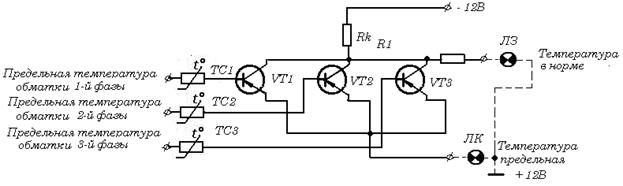

ПРИМЕР. В качестве примера (рис.8.20) использования элемента «ИЛИ - НЕ» приведем схему контроля предельной температуры фазных обмоток эл. двигателя.

При нормальной температуре обмоток электродвигателя сопротивления термодатчиков ТС1-ТС3 велики, транзисторы VT1-VT3 закрыты и горит зеленая лампа ЛЗ. При повышении температуры близкой к предельной одной из обмоток сопротивление термодатчика резко падает и на базе соответствующего транзистора появляется логическая «1», что приводит к открытию соответствующего транзистора. После чего лампа ЛЗ гаснет и загорается лампа ЛК.

Рисунок 8.20. Контроль предельной температуры обмоток

электродвигателя..

На основании универсальных логических элементов «И-НЕ», «ИЛИ-НЕ» можно реализовать любые логические функции, например «И», «ИЛИ», «НЕ» и другие, приведенные на рисунке 8.21, а, б.

Рисунок 8.21. Реализация функций И, ИЛИ, НЕ:

а) на логических элементах И-НЕ; б) на логических элементах ИЛИ-НЕ.

Как правило, построение и расчет любой схемы осуществляется, с начиная ее выхода.

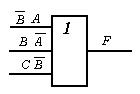

Допустим задано булево выражение :

F =`B A + B`A + C`B.

Первый этап: выполняется логическое сложение, логическая операция «ИЛИ», считая входными переменными функции `B A, B`A и C`B:

Рисунок 8.22. Первый этап комбинации.

Второй этап: к входам элемента «ИЛИ» подключаются логические элементы «И», входными переменными которых являются уже A, B, C и их инверсии:

Рисунок 8.23. Второй этап комбинации.

Третий этап: для получения инверсий `A и`B на соответствующих входах ставят инверторы:

8.24.Третий этап комбинации.

Данное построение основано на следующей особенности, – поскольку значениями логических функций могут быть только нули и единицы, то любые логические функции могут быть представлены как аргументы других более сложных функций.

Таким образом, построение комбинационной логической схемы осуществляется с выхода ко входу.

8.5. Типовые функциональные схемы.

На базе логических элементов можно построить различные генераторы импульсов. Наиболее широкое применение в цифровых устройствах нашли два типа – несимметричный и симметричный мультивибраторы. Но также часто применяются и одновибраторы.

В н е с и м м е т р и ч н о м м у л ь т и в и б р а т о р е (рис. 8.25, а) резистор R выводит в усилительный режим первый инвертор, а выходное напряжение этого инвертора должно удерживать в режиме усиления второй инвертор. Положительная обратная связь через конденсатор С вызовет мягкое (не нуждающееся в первоначальном толчке) самовозбуждение автоколебательного релаксационного процесса. Период Т импульсов, вырабатываемых мультивибратором, определяется в первом приближении постоянной времени t = RC (Т = а t, где а обычно имеет значение 1...2). Частоту следования импульсов можно оценить (с точностью до 10 %) из выражения f = 1/2RC.

Рисунок 8.25. Мультивибраторы:

а) несимметричный; б) симметричный

Схема с и м м е т р и ч н о г о м у л ь т и в и б р а т о р а показана на рис. 8.25,б. Симметричность выходных импульсов может быть достигнута при выполнении условий: R1 = R2; C1 = C2. Период следования импульсов Т определяется как сумма двух времен заряда конденсаторов, т.е.

,

,

где

.

.

Значения t1 и t2 определяются с учетом выходных сопротивлений инверторов Rвых Э1 , Rвых Э2

Частота следования выходных импульсов симметричного мультивибратора определяется из соотношения:

О д н о в и б р а т о р ы предназначены для вырабатывания одиночных импульсов с заданной длительностью. При этом длительность запускающего импульса особой роли не играет, лишь бы она была не больше длительности вырабатываемого одновибратором импульса, т.е. tи зап<tи, где tи зап - длительность запускающего импульса; tи - длительность выходного импульса одновибратора.

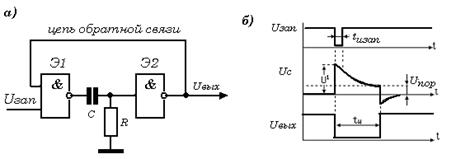

Схема одновибратора приведена на рис. 8.26,а. Он выполнен на двух элементах логики типа «2И-НЕ» путем введения положительной обратной связи (выход второго элемента соединен с входом первого).

Рисунок 8.26. Одновибратор:

а) схема; б) временные диаграммы.

В исходном состоянии на выходе элемента Э2 имеется уровень «1», а на выходе элемента Э1- «0», так как на обоих его входах имеется «1»(запускающие импульсы представляют отрицательный перепад напряжения). При поступлении на вход запускающего отрицательного перепада напряжения на выходе первого элемента появится уровень «1», т.е. положительный скачок, который через конденсатор С поступит на вход второго элемента. Элемент Э2 инвертирует этот сигнал и уровень «0» по цепи обратной связи подается на второй вход элемента Э1. На выходе элемента Э2 поддерживается уровень «0» до тех пор, пока не зарядится конденсатор С до уровня Uc пор = U1 - Uпор, а напряжение на резисторе R не достигнет порогового уровня Uпор (рис. 8.26, б).

Длительность выходного импульса одновибратора может быть определена с помощью выражения

,

,

где Rвых - выходное сопротивление первого элемента. Uпор - пороговое напряжение логического элемента.

|

П Р И М Е Р. Использование мультивибраторов в судовой электронике имеет широкий аспект. Рассмотрим один из них. На рис. 8.27 приведена принципиальная схема электрон-ной сирены, собранной на одном транзисторе и микросхеме. По существу, схема состоит из трех генераторов с различными временными характеристиками. Так. транзистор V1, элемент D1.1, конденсатор С1 и резисторы R1 - R3 образуют генератор с тактовой частотой около 1Гц. Желаемая частота повторения сигналов может быть подобрана подстро-ечными резисторами R2 и R3. Элемент D1.3, резистор R4. конденсатор С2 и элемент D1.4 составляют второй генератор с частотой генерации около 1000 Гц. И наконец, элемент D1.3 вместе с резистором R5, конденсатором C3 и элементом D1.4 образуют третий генератор, но уже более низкой частоты, около 200 Гц. Оконечной нагрузкой сирены является динамик В1, подключенный к выходу элемента D 1.4.

П Р И М Е Р. Использование мультивибраторов в судовой электронике имеет широкий аспект. Рассмотрим один из них. На рис. 8.27 приведена принципиальная схема электрон-ной сирены, собранной на одном транзисторе и микросхеме. По существу, схема состоит из трех генераторов с различными временными характеристиками. Так. транзистор V1, элемент D1.1, конденсатор С1 и резисторы R1 - R3 образуют генератор с тактовой частотой около 1Гц. Желаемая частота повторения сигналов может быть подобрана подстро-ечными резисторами R2 и R3. Элемент D1.3, резистор R4. конденсатор С2 и элемент D1.4 составляют второй генератор с частотой генерации около 1000 Гц. И наконец, элемент D1.3 вместе с резистором R5, конденсатором C3 и элементом D1.4 образуют третий генератор, но уже более низкой частоты, около 200 Гц. Оконечной нагрузкой сирены является динамик В1, подключенный к выходу элемента D 1.4.

Т р и г г е р – это логическая схема с положительной обратной связью, могущая неограниченно долго находиться в одном из двух устойчивых состояний («0» и «1» ), которые обеспечиваются положительной обратной связью а не входным сигналом. Триггер скачком, лавинообразно меняет одно состояние на другое под воздействием входного сигнала.

Триггеры делятся на симметричные и несимметричные (триггеры Шмидта). Триггеры Шмидта рассматриваются как импульсные устройства, а симметричные делятся :

1. По способу записи информации на:

а) асинхронные,

б) синхронные (тактируемые).

2. По способу управления записью информации на:

а) статические,

б) динамические – по фронту переднему или заднему,

в) двухступенчатые – по двум фронтам.

3. По способу организации логической связи :

а) элементарные с раздельной установкой «0» и «1» – RS–триггеры

б) с приемом информации по одному входу – D–триггеры

в) со счетным входом – T–триггеры

г) универсальные с раздельной установкой «0» и «1» – JK–триггеры

д) комбинированные ( смешанные )

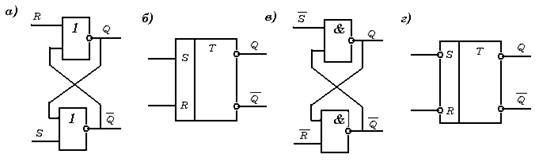

А с и н х р о н н ы й RS – т р и г г е р (рис.8.28) имеет два выхода : прямой и инверсный. Перевод триггера в состояние Q=1 называют установкой (set) и вход, по которому это осуществляется, обозначается S.

Перевод триггера в нулевое состояние Q=0 называют сбросом (reset) и вход сброса обозначают R. Триггер является асинхронным, если его переключение происходит в момент поступления управляющих сигналов.

Рисунок 8.28. Асинхронный RS – триггер:

а) триггер на логическом элементе ИЛИ-НЕ; б) условное обозначение; в) триггер на логических элементах И-НЕ;

г) условное обозначение.

При состоянии на входах S=1, R=0 состояние на выходе соответствует единице (Q = 1; Ō = 0 ), при S = 0; R = 1 соответствует нулю (Q = 0; Ō = 1 ).

При состоянии на входах S=1, R=0 состояние на выходе соответствует единице (Q = 1; Ō = 0 ), при S = 0; R = 1 соответствует нулю (Q = 0; Ō = 1 ).

При нулевом значении сигналов на входах триггера состояние на выходе не изменяется, а при единичных значениях сигналов на входах состояние на выходе принимают неопределенного значения.

Триггер еще можно назвать устройством с обратными связями. На рисунке 8.28,а изображена схема триггера на логических элементах «ИЛИ-НЕ». Такая схема называется асинхронным RS-триггером. Первый (сверху) выход называется прямым, второй - инверсным. Если на оба входа (R и S) подать логические. нули, то состояние выходов определить невозможно. Триггер установится как ему заблагорассудится, т. е. в произвольное состояние. Допустим, на выходе Q присутствует логическая «1», тогда на нижнем выходе обязательно будет логический «0». И наоборот. Чтобы установить триггер в нулевое состояние (когда на прямом выходе логический. «0», а на инверсном - логическая «1») достаточно на вход R подать напряжение высокого уровня. Если высокий уровень подать на вход S, то это переведет его в состояние «1», или как говорят, в единичное состояние (на прямом выходе логическая «1», на инверсном - логический «0»). И в том, и в другом случаях напряжение соответствующего уровня может быть очень коротким импульсом - на грани физического быстродействия микросхемы. То есть, триггер обладает двумя устойчивыми состояниями, причем эти состояния зависят от ранее воздействующих сигналов, что позволяет сделать следующий вывод - триггер является простейшим элементом памяти.

RS-триггер можно собрать и на элементах «И-НЕ», как показано на рисунке 8.28, в, г.Такая конструкция встречается довольно часто. Принцип работы такой же, как у триггера на элементах «ИЛИ-НЕ», за исключением инверсии управляющих сигналов, т. е. установка и сброс триггера производится не логическая «1», а логический «0». Другими словами, входы такого триггера инверсные. В описанных триггерах изменение состояния происходит сразу после изменения состояния на входах R и S. Поэтому такие триггеры называются асинхронными.

С и н х р о н н ы й RS – т р и г г е р изображен на рисунке 8.29,а В таком триггере вводится дополнительный вход С, называемый тактовым или синхронизирующим. Изменение состояний триггера происходит при подаче сигналов логической «1» на входы R и S и последующим воздействием на вход С тактового (синхронизирующего) импульса. Если на тактовый вход импульс

Рис. 8.29 Триггеы на логических элементах И-НЕ:

а) синхронный; б) условное обозначение; в) D – триггер; г) условное обозначение.

не воздействует, то состояние триггера не изменится. Другими словами, изменение состояния триггера происходит под действием синхроимпульса, поэтому такие триггеры называются синхронными.

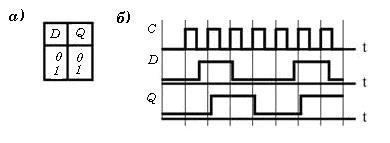

D – т р и г г е р отличается от синхронного RS-триггера тем, что у него только один информационный вход D. D-триггер показан на рисунке 8.29,б. D-триггер (от английского DELAY) называют информационным триггером, также триггером задержки. D - триггер бывает только синхронным. Он может управляться (переключаться) как уровнем тактирующего импульса, так и его фронтом. Для триггера типа D, состояние в интервале времени между сигналом на входной линии и следующим состоянием триггера формируется проще, чем для любого другого типа.

Рисунок 8.30. D – триггер: а) таблица управления; б) временные диаграммы

Если на вход D подать логическую единицу, затем на вход С подать импульс, то на выходе Q (прямой выход) установится логическая «1». Если на вход D подать логический «0», на С импульс, то на Q установится логический «0». Т. е. D-триггер осуществляет задержку информации, поступающей на вход D. При чем эта информация хранится в D-триггере, пока не придет следующий бит («0» или «1») информации. По сути это ячейка памяти.

Если вход D замкнуть с инверсным выходом, то останется только один вход С. При подаче на вход С импульса триггер переключится, т. е. если на выходе был логический «0», то станет логической «1». При следующем импульсе триггер снова переключится, т. е. логическая «1» сменится логическим «0». Таким образом, триггер осуществляет деление частоты входных импульсов на 2 (ведь уровень сигнала на выходе меняется в два раза реже). В таком режиме D-триггер называют счетным или Т-триггером. Этот режим (режим деления частоты) используется довольно широко.

J K – т р и г г е р а имеет три входа - J, K, C (рис.8.31). Вход J вместо R, вход К вместо S, С так и остается - синхронизацией. Если на вход J подана логическую «1», на К - логический «0» или наоборот, то он работает как синхронный RS-триггер, если на оба входа J и К поданы логические «1», то он работает как счетный Т-триггер. Триггер имеет по три входа J и K, связанных операцией «И», а также асинхронные входы Ra и Sa для установки триггера в состояние «1» и «0» независимо от сигналов на информационных и синхронизирующем входах.

Асинхронная установка триггера в единичное или нулевое состояние производится импульсами низкого уровня (логический «0» приположительной логике), поступающими на входы Ra или Sa. Состояниевходов J, K и С при асинхронном управлении безразлично. В отличии от RS-триггера здесь одновременная подача переключающих сигналов на входы Ra и Sa допустима. Когда эти входы не задействованы, на них следуетподдерживать напряжение высокого уровня.

Таблица состояний триггера К155ТВ1 приведена в табл. 8.2. Символ означает, что синхроимпульс С изменяется от низкого уровня до высокого уровня (перепад «0»,»1»); символ ¯ означает, что синхроимпульс С изменяется от высокого уровня до низкого уровня (перепад «1»,»0»).

Таблица 8.2.

Таблица переключений триггера К155ТВ1

| Sa | Ra | Jn | Kn | C | Qn+1 | Режим |

| 1 | 1 | x | x | | Qn | хранение |

| 1 | 1 | 0 | 0 | ¯ | Qn | хранение |

| 1 | 1 | 0 | 1 | ¯ | 0 | синхронный |

| 1 | 1 | 1 | 0 | ¯ | 1 | синхронный |

| 1 | 1 | 1 | 1 | ¯ | Qn | синхронный |

| 1 | 0 | x | x | x | 0 | асинхронный |

| 0 | 1 | x | x | x | 1 | асинхронный |

| 0 | 0 | x | x | x | Qn=Qn =1 | асинхронный |

JK - триггеры относятся к универсальным устройствам. Их универсальность имеет двойственный характер.

JK - триггеры относятся к универсальным устройствам. Их универсальность имеет двойственный характер.

Рис.8.31. Структурная схема синхронного JK триггера

Во первых, эти триггеры с равным успехом могут быть использованы в различных цифровых устройствах: регистрах, цифровых счётчиках, делителях частоты и т.д., во вторых, путём определённого соединения выводов они легко обращаются в триггеры других типов. Структурная схема JK-триггера с динамическимуправлением приведена на рис. 8.31.

D - триггер может быть получен из JK - триггера с помощью дополнительного инвертора (рис.8.32,а)

Рисунок 8.32. Триггеры на базе JK.

а) D-триггер; б) Т-триггер.

Т – т р и г г е р - это счетный триггер. Т-триггер имеет один вход (вспомогательные входы принудительной установки “0” и “1” не рассматриваются), куда подают тактирующие (счетные) импульсы (рис.8.32,б). После подачи каждого тактирующего импульса состояние Т-триггера меняется в обратное (инверсное) предыдущему состоянию (аналогично состоянию JK-триггера при комбинации входных переменных J=1 и K=1). Т-триггеры строятся только на базе двухступенчатых (RS, D, JK) триггеров.

Т-триггер можно синтезировать из любого типа двухступенчатого триггера. Рассмотрим пример синтеза Т-триггера из JK-триггера. Для этого Т-триггер представим как совокупность комбинационного устройства КУ и JK-триггера (рис.8.33).

Рисунок 8.33. Функциональная схема Т–триггера и таблица его состояния.

Приведенное на рис.8.33,а комбинационное устройство должно обеспечить на выходах J и K соответствующие сигналы управления RS-триггером (при подаче на его входы сигналов Q и Т), в соответствии с таблицей состояний (рис. 8.33, б).

Т р и г г е р Ш м и д т а - это специфический вид триггера, имеющего один вход и один выход. Такой триггер еще называют несимметричным. В триггере Шмидта переход из одного устойчивого состояния в другое осуществляется при определенных уровнях входного напряжения, называемых пороговыми уровнями. Триггер Шмидта изображен ниже (рис. 8.34).

Если на вход триггера Шмидта подавать нарастающее напряжение (нижний график рис. 8.34,б), то при некотором уровне Uп1 в момент t1 напряжение на выходе скачком переходит из состояния «0» в состояние «1». Если уменьшать напряжение на входе до некоторого напряжения Uп2 в момент t2 напряжение на выходе скачком переходит из состояния «1» в состояние «0». Явление несовпадения уровней Uп1 и Uп2 называется гистерезисом. Соответственно, передаточная характеристика триггера Шмидта обладает гистерезисным характером. Триггер Шмидта, в отличие от других триггеров, не обладает памятью и используется для формирования прямоугольных импульсов из напряжения произвольной формы.

Рисунок 8.34. Триггер Шмидта:

а) схема; б) графики принципа работы.

Триггеры используются довольно широко как самостоятельные устройства, так и в качестве основы для более сложных устройств - счетчиков, регистров, запоминающих устройств. В финале поглядим на типичную схему использования RS-триггера (рис. 8.35)

Триггеры используются довольно широко как самостоятельные устройства, так и в качестве основы для более сложных устройств - счетчиков, регистров, запоминающих устройств. В финале поглядим на типичную схему использования RS-триггера (рис. 8.35)

|

Следует помнить, что RS-триггеры в ТТЛ-микросхемах (серии 133, 155, 1533, 531 и пр.) управляются логическим «0», в КМОП-микросхемах (серии 176, 561, 564, 1564 и пр.) - логической «1».

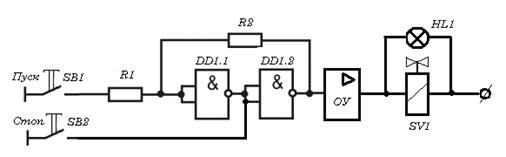

ПРИМЕР. В качестве пускового устройства электромагнитного клапана используем триггер как элемент памяти, собранный на двух логических элементах «И» с обратной связью через резистор R2 (рис. 8.36).

8.36. Пусковое устройство электромагнитного клапана.

Электромагнитный клапан может стоять на любой судовой жидкостной системе и управляться дистанционно. Для подачи питания на клапан нажимаем кнопку «Пуск» (SB1) и на выходе элемента DD1.1 получаем логический «0», а на выходе элемента DD1.2 – логическую «1», которая возвращается на вход элемента DD1.1 и кнопу SB1 можно отпускать. Через операционный усилитель

получают питание сигнальная лампа HL1 и катушка электромагнитного клапана.

Для обесточивания катушки клапана и сигнальной лампы достаточно нажать кнопку SB2. На вход элемента DD1.2 поступает логическая «1», следовательно, на выходе образуется логический «0», который также поступает на вход элемента DD1.1. Таким образом «обнуляется» элемент памяти. Кнопу «Стоп» можно отпускать. Катушка электромагнитного клапана и сигнальная лампа обесточиваются.

Р е г и с т р о м (to register - регистрировать) называют цифровое устройство, предназначенное для записи и хранения числа. Регистры обладают большими функциональными возможностями. Они используются в качестве управляющих и запоминающих устройств генераторов и преобразователей кодов, счетчиков, делителей частоты, узлов временной задержки .

Элементами структуры регистров являются синхронные триггеры D, RS или JK - типа с динамическим или статическим управлением. Так как одиночный триггер может запомнить один разряд (бит) двоичной информации, то его можно считать одноразрядным регистром. Для запоминания многоразрядных чисел используют "линейки " из нескольких триггеров - по количеству разрядов чисел. В схемы регистров входят также комбинационные элементы, роль которых в данном случае вспомогательная.

Занесение информации в регистр называют операцией ввода или считывания. Запись информации в регистр не требует его предварительного обнуления (сброса).

Все регистры в зависимости от функциональных свойств подразделяются на две категории : накопительные регистры (памяти, хранения) и сдвиговые .

В свою очередь сдвиговые регистры делятся: по способу ввода и вывода информации - на параллельные, последовательные и комбинированные (параллельно-последовательные и последовательно-параллельные); по направлению передачи (сдвига) информации - на однонаправленные и реверсивные.

Р е г и с т р ы п а м я т и - простейший вид регистров. Их назначение - хранить двоичную информацию небольшого объема в течение промежутка времени. Эти регистры представляют собой набор синхронных триггеров , каждый из которых хранит один разряд двоичного числа.

Рис. 8.37 - Регистр памяти (хранения) на D-триггерах.

Ввод (запись, загрузка) и вывод (считывание) информации производится одновременно во всех разрядах параллельным кодом. Запись обеспечивается тактовым импульсом. С приходом очередного тактового импульса происходит обновление записанной информации.

Структура регистра памяти (хранения) на D-триггерах показана на рисунке 8.37. Каждый триггер служит для хранения одного разряда числа. Вход R служит для установки триггеров в нулевое состояние перед записью информации. Входное двоичное число подается на входы D0-D2 и при подаче импульса на вход С в триггеры записывается этот код, т. е. информация. Эта информация может храниться сколь угодно долго, если на вход С не поступают импульсы (или если не исчезнет питание). Информация может выводиться как в прямом (с прямых выходов триггеров), так и в инверсном коде (с инверсных выходов).

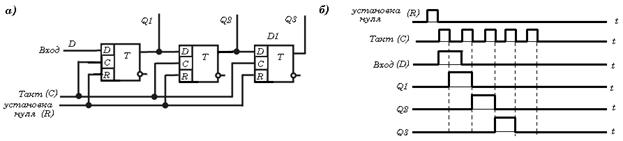

Р е г и с т р с д в и г а - другая разновидность регистров. Регистр сдвига предназначен для преобразования информации путем ее сдвига под воздействием тактовых импульсов. Посмотрим на структуру регистра сдвига на D-триггерах:

Рис. 8.38 - Регистр сдвига на D-триггерах:

а) схема; б) диаграмма

Как видно из рисунка 8.38,а в регистре сдвига также объединяются входы R и C триггеров. Перед записью информации регистр устанавливается в нулевое состояние. Информация подается на D-вход первого триггера. При подаче импульса на вход С бит информации (логический «0» или логическая «1») записывается в триггер. При подаче следующего импульса этот бит записывается в следующий триггер. При этом в первый триггер записывается следующий бит информации и т. д. Другими словами, при воздействии тактовых импульсов информация продвигается по регистру от первого триггера к последнему. При заполнении всех триггеров число в параллельном коде можно вывести с выходов Q0-Q2. При этом первый бит информации будет присутствовать на выходе Q2, второй - на выходе Q1 и т. п.

Показанный на рисунке регистр сдвигает информацию только в одну сторону. Такие регистры называют регистром со сдвигом вправо или регистр со сдвигом влево (смотря куда он сдвигает). Существуют регистры, сдвигающие информацию в обе стороны. Направление сдвига определяется управляющим сигналом, подаваемым на специальный вход.

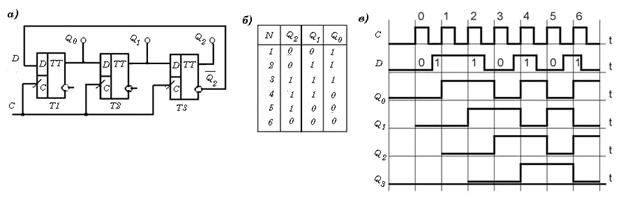

ПРИМЕР. В качестве примера приведем схему кольцевого счетчика, использующего для обегающего контроля параметров судовых механизмов. На судах с классом автоматизации А1 (безвахтенное обслуживание) в обязательном порядке имеет место система автоматического контроля параметров с выводом их на печатающее устройство и включение тревожной сигнализации при выходе параметров за пределы уставок.

На базе регистров сдвига можно построить кольцевые счетчики - счетчики Джонсона. В частности, если счетчик состоит из трех триггеров (m=3), то он будет иметь шесть устойчивых состояний.

Рисунок 8.39. Кольцевой счетчик на D-триггерах:

а) схема трехразрядного счетчика; б) таблица состояния; в) диаграмма.

Рассмотрим схему трехразрядного счетчика, выполненного на базе D-триггеров (регистр сдвига реализован на D-триггерах). Для построения кольцевого счетчика достаточно соединить инверсный выход последнего триггера регистра (последнего разряда) с входом “D” (с входом, предназначенным для ввода последовательной информации) первого триггера (рис. 8.39,а).

Предположим, что вначале все триггеры находятся в состоянии “0”, т.е. Q0= Q1=Q2=0. При этом на входе “D” первого триггера присутствует уровень «1», т.к  =1. Первым синхроимпульсом в триггер Т1 запишется «1», вторым - единица запишется в первый триггер, из первого - во второй и т.д. до тех пор, пока на всех выходах регистра не будет «1».

=1. Первым синхроимпульсом в триггер Т1 запишется «1», вторым - единица запишется в первый триггер, из первого - во второй и т.д. до тех пор, пока на всех выходах регистра не будет «1».

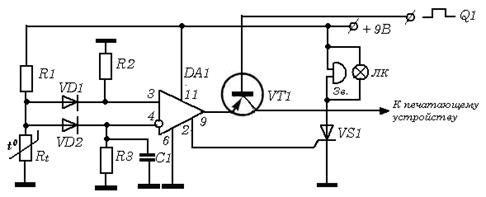

Рисунок 8.40. Сигнальный канал кольцевого счетчика.

При появлении, например, логической «1» на выходе Q1 (рис.8.39,а) этот сигнал подается на базу транзистора VT1 схемы контроля одного из параметров контролируемого механизма (к примеру – температура охлаждающей воды) (см. рис.8.40), который снимает напряжение, соответствующее определенной температуре контролируемой среды, с выхода 9 операционного усилителя DD1, и через эмиттерно-коллекторный переход транзистора VT1 подает этот сигнал на печатающее устройство.

В случае нарушения параметра охлаждающей воды, срабатывает тревожная сигнализация.

После заполнения регистра единицами, на инверсном выходе триггера Т3 появится  =0 и четвертым синхроимпульсом в Т1 запишется логический «0».

=0 и четвертым синхроимпульсом в Т1 запишется логический «0».

После поступления последующих трех синхроимпульсов регистр обнуляется и на его вход “D” снова подается уровень «1». Таким образом, цикл повторения состояния кольцевого счетчика состоит из шести тактов синхросигнала. Как видим, при работе в начале от первого триггера до последнего триггера распространяется “волна единиц”, а затем “волна нулей”.

Ц и ф р о в о й с ч е т ч и к и м п у л ь с о в - это цифровой узел, который осуществляет счет поступающих на его вход импульсов. Результат счета формируется счетчиком в заданном коде и может храниться требуемое время. Счетчики строятся на триггерах, при этом количество импульсов, которое может подсчитать счетчик определяется из выражения N = 2n - 1, где n - число триггеров, а минус один, потому что в цифровой технике за начало отсчета принимается «0». Счетчики бывают суммирующие, когда счет идет на увеличение, и вычитающие - счет на уменьшение. Если счетчик может переключаться в процессе работы с суммирования на вычитание и наоборот, то он называется реверсивным. Коль счетчики строят на триггерах, посмотрим, как все это работает:

Рисунок 8.41. Схема счетчика с последовательным переносом на

Т-триггерах и графики, поясняющие принцип его работы

В качестве исходного состояния принят нулевой уровень на всех выходах триггеров (Q1 - Q3), т. е. цифровой код 000. При этом старшим разрядом является выход Q3. Для перевода всех триггеров в нулевое состояние входы R триггеров объединены и на них подается необходимый уровень напряжения (т. е. импульс, обнуляющий триггеры). По сути это сброс. На вход С поступают тактовые импульсы, которые увеличивают цифровой код на единицу, т. е. после прихода первого импульса первый триггер переключается в состояние «1» (код 001), после прихода второго импульса второй триггер переключается в состояние «1», а первый - в состояние 0 (код 010), потом третий и т. д. В результате подобное устройство может досчитать до 7 (код 111), поскольку 23 - 1 = 7. Когда на всех выходах триггеров установились единицы, говорят, что счетчик переполнен. После прихода следующего (девятого) импульса счетчик обнулится и начнется все с начала. На графиках изменение состояний триггеров происходит с некоторой задержкой tз. На третьем разряде задержка уже утроенная. Увеличивающаяся с увеличением числа разрядов задержка является недостатком счетчиков с последовательным переносом, что, несмотря на простоту, ограничивает их применение в устройствах с небольшим числом разрядов.

ПРИМЕР. В качестве примера приведем схему электронного замка подачи питания на сепаратор льяльных вод во избежание случайного включения установки в особых зонах мирового океана (рис. 8.42). Его особенность - необычный ввод кодовых чисел (повторными нажатиями на кнопки), что повышает "секретность"замка.

Рисунок 8.42. Электронный замок подачи питания на сепаратор льяльных вод.

Замок прост в эксплуатации, не требует налаживания, некритичен к параметрам источника питания. В ждущем режиме потребляет очень мало энергии. Защита замка от несанкционированного доступа обеспечивается применением счетчиков импульсов (10 000 комбинаций) и введением таймера, ограничивающего время набора кода.

Схема замка показана на рисунке 8.42. По функциональному назначению устройство можно условно разбить на четыре части. Первая - блок набора кода (элементы DD1, DD3-DD6, DD7.1); вторая - элементы установки счетчиков в исходное состояние и таймер (DD2.1-DD2.3, DA1); третья часть - исполнительная (элементы DA2, VT2, VS1, K1) и четвертая - блок питания.

При кратковременном нажатии на кнопку SB5 происходит установка счетчиков DD3-DD6 в нулевое состояние и запуск таймера DA1. Последующие нажатия этой кнопки на работу таймера не влияют, но позволяют сбросить показания при ошибке в наборе. Набор кода необходимо произвести за время t=1,1xR11xC1, где R11 - сопротивление резистора в мегаОмах, C11- емкость конденсатора в микрофарадах, t - время в секундах. Сопротивление резисторов R11, R12 может быть в пределах 10...100 кОм. По прошествии времени t на выходе таймера DA1 (вывод 3) возникает низкий уровень и происходит установка счетчиков в исходное состояние.

Программирование кода осуществляют распайкой соответствующих перемычек. Набирают код нажатием на соответствующую кнопку (SB1-SB4) заданное число раз. Предположим, что установлен код замка 1952 (показан на схеме). Тогда на первую кнопку следует нажать 1 раз, на вторую - 9, на третью - 5, на четвертую - 2 раза. Кнопки подключены к счетч

Дата добавления: 2020-10-14; просмотров: 274;