ПРЕОБРАЗОВАТЕЛИ КОДОВ

14.1 Преобразователи двоично-десятичного кода в код

управления семисегментным индикатором

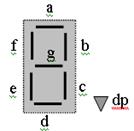

На рисунке 14.1 приведено стандартное обозначение сегментов семисегментных преобразователей.

Сегменты обозначаются латинскими буквами a, b, c, d, e, f, g, а точка – dp (Decimal Point – десятичная точка). Управляют работой такого индикатора специальные дешифраторы-преобразователи: К514ИД1, КР514ИД2, 514ПП1, К514ИД4, К514ПР1, 155ПП5, 533ИД19, К564ИД5.

Микросхемы К514ИД1 и К514ИД14 имеют открытые выходы и резисторы в коллекторных цепях. Они используются для управления индикаторами с общим катодом без внешних резисторов.

Функционирование микросхемы К514ИД1А, Б, В описывается таблицей истинности (таблица 14.1). Судя по таблице, нулевое напряжение на выходе отвечает выключенному состоянию сегмента. Все сегменты оказываются выключенными при подаче на все информационные входы высокого напряжения.

Рисунок 14.1 – Обозначение сегментов семисегментных преобразователей

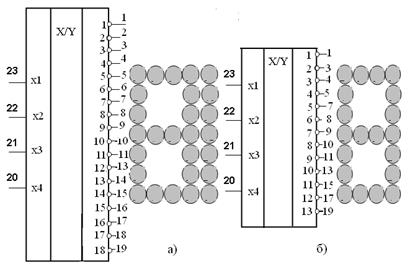

Рисунок 14.2 – Графическое обозначение:

а − КР514ИД1; б − КР514ИД2

Управление работой преобразователя осуществляется по входу BI. Уровень лог. 1 на входе BI разрешает работу ИС 514ИД1, лог. 0на этом входе приводит к обнулению всех выходов. Выходы преобразователя организованы по схеме с открытым эмиттером, причем величина выходных токов не более 4,6 мА. В отличие от 514ИД1 микросхема 514ИД2, имеет на выходах формирователи с открытыми коллекторами, обеспечивающими ток в нагрузке до 20 мА (нагрузка включается между питанием и выходом коллектора). Выходные сигналы ИС 514ИД2 инверсны по отношению к выходным сигналам ИС 514ИД1. Вход BI выполняет ту же функцию, что и в 514ИД1.

Дешифратор-преобразователь ИС 514ПП1 по назначению и принципу управления аналогичен КР514ИД2 (514ИД2). Преобразователь кода ИС К155ПП5 выполняет ту же функцию, что и 514ИД2, отличие заключается лишь в том, что разрешение по выходу осуществляется низким уровнем сигнала по входу  .

.

Таблица 14.1 – Таблица истинности К514ИД1

Микросхема К514ИД4 А, Б, В – это дешифратор-преобразователь с памятью (рисунок 14.3), в таблице 14.2 представлена таблица истинности К514ИД4А, Б, В, служащий для управления семисегментным индикатором. Особенностью дешифратора является наличие внутренней регистровой памяти, позволяющей хранить входную информацию после снятия данных со входа D1. Фиксация данных происходит при WR = 1, BI = 0. В случае, если WR = BI = 0, реализуется режим преобразования без запоминания. Для гашения сегментов на вход BI следует подать уровень логической «1» при любом состоянии входа WR. Соответствие между входными и выходными кодами дешифратора показано в таблице истинности, где нуль на выходе соответствует выключенному состоянию сегмента. Дешифратор − преобразователь 514ИД4В вследствие тносительно большого выходного тока (до 52 мА при Uвых = 1,7 В) может быть использован для параллельного управления несколькими индикаторами. В конкретных ситуациях выходы дешифраторов-преобразователей можно умощнить, подключая их к нагрузке через токовые ключи 514К.

Таблица 14.2 – Таблица истинности К514ИД4А,Б,В

Микросхема К555ИД18 (рисунок 14.4) – преобразователь двоично-десятичного кода 1-2-4-8 в сигналы управления семисегментным индикатором.

Рисунок 14.3 – Условное изображение

Рисунок 14.4 –Условное изображение ИС К555ИД18

Он имеет выходы с открытым коллектором и предназначен для управления полупроводниковыми индикаторами с общим анодом, которые подключаются через ограничительные резисторы Rогр. Особенность микросхемы – возможность гашения левых незначащих нулей при индикации многоразрядных чисел и возможность одновременного включения всех сегментов индикатора для контроля его исправности. Для обеспечения указанных режимов используют входы E0, K и двунаправленный вывод Е. Обычный режим преобразования входного кода осуществляется при подаче на входы E0 и K лог. 1. Вывод E можно при этом оставить свободным – в состав микросхемы входит резистор сопротивлением около 5 кОм, включенный между выводом Е и цепью + 5 В. Если на вывод E подать лог. 0, независимо от состояния всех входов происходит гашение всех сегментов индикатора подключенного к выводам микросхемы. Если на вывод E подать лог. 1 или оставить его свободным, а на вход К (контроль) подать лог. 0, то независимо от сигналов на других входах включаются все сегменты индикатора. Особый режим осуществляется при подаче на вход К лог. 1, на вход Е – лог. 1 (вход свободен) и на вход Е0 (гашение) – лог. 0. В этом случае при подаче на входы 1-2-4-8 двоичного кода, соответствуещего цифрам 1 – 9, происходит индикация этих цифр, при подаче кода цифры 0 – гашение индикатора и выдача на выход Е лог. 0.

Поэтому при совместной работе нескольких индикаторов этот сигнал можно использовать для гашения незначащих нулей соседних индикаторов, если вывод Е данного индикатора соединить со входом Е0 соседнего разряда.

14.2 Преобразователи кода для неполных матричных

индикаторов

Микросхемы КМ155ИД8А, КМ155ИД8Б, КМ155ИД9 – преобразователи двоично-десятичного кода 1-2-4-8 в коды работы индикаторов, состоящих из 27 отдельных светодиодов (ИД8, рисунок 14.5) и из 20 светодиодов для 155ИД9. Микросхемы имеют по 4 входа для подачи входного кода. Число выходов микросхемы КМ155ИД8 составляет 18, микросхемы КМ155ИД9 – 13. К каждому выходу микросхем должны быть подключены один или два последовательно включенных светодиода, соединенных с источником питания + 5 В. На рисунках 14.5 а, б на элементах индикаторов указаны номера выводов микросхем, к которым должны быть подключены светодиоды индикаторов. Микросхемы выполнены с открытым коллекторным выходом и содержат ограничительные резисторы двух номиналов (для выходов, стыкуемых с двумя последовательно включенными светодиодами, номинал ограничительного резистора меньше, чем для выходов, нагружаемых одним диодом) – что обеспечивает одинаковый ток через все светодиоды индикатора – 10 мА для микросхем КМ155ИД8А и КМ155ИД9 и 15 мА для КМ155ИД8Б. Для входных кодов чисел 0–9 на светодиодах индицируются соответствующие цифры, для кода числа 10 – знак «–», для кода числа 11 – буква Е, для кодов чисел 12–15 все светодиоды индикаторов погашены.

При необходимости можно увеличить число диодов в индикаторах на один или два в каждом сегменте индикации. При этом надо руководствоваться правилом: для цепочки из трех светодиодов напряжение питания должно быть увеличено до 7 В, а для четырех светодиодов – до 9 В. Одиночные светодиоды должны быть по-прежнему подключены к источнику питания + 5 В.

а − МCX К155ИД8; б − МCX К155ИД9

Рисунок 14.5 – Подключение выводов к светодиодам индикатора

14.3 Преобразователи кода для шкальных индикаторов

Микросхема КМ155ИД11- преобразователь двоичного кода в код управления светодиодной шкалой, формирующей светящийся столбик, число светящихся точек в котором равно числу соответствующему входному коду (рисунок 14.6). Микросхема имеет три входа 1, 2, 4 для подачи входного кода, вход разрешения  , вход переноса P0, восемь выходов для подключения светодиодной шкалы 0 – 7 и выход переноса Р1. Работа этой микросхемы описывается функциями:

, вход переноса P0, восемь выходов для подключения светодиодной шкалы 0 – 7 и выход переноса Р1. Работа этой микросхемы описывается функциями:

где Кi = x3x2x1 – минтермы, i = 0..7.

Рисунок 14.6 – Условное обозначение ИС КМ155ИД11, КМ155ИД13

В частности, при m £ 7 и Р0 = 1, Е = 1 (  ) функции

) функции  и fm = 1, Р1 = 0. Т.е. при подаче на вход Р0 лог. 1 и на вход Е лог. 0 напряжение высокого уровня появляется на том выходе микросхемы, номер которого соответствует десятичному эквиваленту кода на входах А1, А2, А4 и на всех выходах с меньшим номером, при этом на выходе Р1 – лог. 0. Если на вход Р0 подать лог.0, на выходах 0 – 7 будет лог. 1, на выходе Р1 – лог. 0, независимо от сигналов на входах Е и А1, А2, А4. Если на входах Р и Е – лог.1, на выходах 0 – 7 – лог.0, на выходе Р1 – лог.1. При подаче на вход Е высокого уровня напряжения (лог. 1), а на вход Р1 лог. 0, на первых семи выходах микросхемы будет напряжение низкого уровня, а на восьмом и выходе переноса будет действовать напряжение высокого уровня.

и fm = 1, Р1 = 0. Т.е. при подаче на вход Р0 лог. 1 и на вход Е лог. 0 напряжение высокого уровня появляется на том выходе микросхемы, номер которого соответствует десятичному эквиваленту кода на входах А1, А2, А4 и на всех выходах с меньшим номером, при этом на выходе Р1 – лог. 0. Если на вход Р0 подать лог.0, на выходах 0 – 7 будет лог. 1, на выходе Р1 – лог. 0, независимо от сигналов на входах Е и А1, А2, А4. Если на входах Р и Е – лог.1, на выходах 0 – 7 – лог.0, на выходе Р1 – лог.1. При подаче на вход Е высокого уровня напряжения (лог. 1), а на вход Р1 лог. 0, на первых семи выходах микросхемы будет напряжение низкого уровня, а на восьмом и выходе переноса будет действовать напряжение высокого уровня.

Выходы микросхемы КМ155ИД11 выполнены с открытым эмиттером и ограничительным резистором в цепи коллектора, обеспечивающим выходной ток для непосредственного подключения светодиодов между выходами и общим проводом. При работе одной микросхемы с восемью светодиодами высота «столбика» светящихся светодиодов будет на единицу больше десятичного эквивалента кода на входах А1, А2, А4. Микросхема КМ155ИД13 имеет те же выводы, что и КМ155ИД11, но иную логику работы. Она обеспечивает построение шкал, в которых светятся одновременно два рядом расположенных диода – один с номером, равным эквиваленту, а второй – с номером на единицу больше. При подаче на вход Р0 лог.1, а на вход  лог. 0 входному коду 000 соответствует лог. 1на выходе0, входному коду001 – лог. 1на выходах 0 и 1, коду 010 – лог.1 на выходах 1 и 2 и т.д. Кроме того, входному коду 000 и лог. 0 на входе

лог. 0 входному коду 000 соответствует лог. 1на выходе0, входному коду001 – лог. 1на выходах 0 и 1, коду 010 – лог.1 на выходах 1 и 2 и т.д. Кроме того, входному коду 000 и лог. 0 на входе  соответствует лог. 0 на выходе Р1 (во всех остальных случаях на выходе Р1 – лог. 1). Лог. 0 на входе Р0 включает светодиод, подключенный к выходу 7, независимо от всех других сигналов, этот вход не влияет ни на какие другие выходы. Работа ИС описывается функциями:

соответствует лог. 0 на выходе Р1 (во всех остальных случаях на выходе Р1 – лог. 1). Лог. 0 на входе Р0 включает светодиод, подключенный к выходу 7, независимо от всех других сигналов, этот вход не влияет ни на какие другие выходы. Работа ИС описывается функциями:

fi = E( Ki V Ki+1), i = 0...6;  .

.

где Кi = x3x2x1 – минтермы, i = 0 ... 7. Сигналы  , Р0 и Р1 используются для наращивания шкального индикатора.

, Р0 и Р1 используются для наращивания шкального индикатора.

ТРИГГЕРЫ

15.1 Общие положения

Триггером называют устройство, которое может находиться в одном из двух устойчивых состояний, например, включен – «1», выключен – «0» и регенеративно (скачком) переходить из одного состояния в другое. Способность триггера фиксировать на любое время свое текущее состояние наделяет его свойством памяти. Вследствие чего триггер является простейшим последовательностным устройством (в дальнейшем будем именовать устройствами последовательного действия), поскольку его состояние в новом такте определяется не только комбинацией входных сигналов, но и исходным, текущим состоянием.

Триггеры являются одним из самых распространенных схемотехнических элементов в цифровой и вычислительной технике и широко применяются в виде самостоятельных изделий и в качестве базовых элементов для построения регистров, счетчиков, запоминающих устройств. Триггеры существенно различаются между собой по схемному исполнению, выполняемым функциям, способам управления, электрическим параметрам. Простейшую триггерную ячейку можно представить в виде двухкаскадного усилителя постоянного тока, охваченного петлей положительной обратной связи (рисунок 15.1).

Причем усилительные каскады D1, D2 должны быть инвертирующими и иметь релейную передаточную характеристику, т.е. должны работать в ключевом режиме: при нулевом напряжении на входе (лог. 0) – единичное напряжение (лог. 1) на выходе и наоборот. Предположим, что в момент включения питания на выходе первого усилительного каскада D1 установилось единичное напряжение, тогда на выходе D2 будет нулевое напряжение.

а − состояние «включено»; б − состояние «выключено»;

в − логическая структура

Рисунок 15.1 – Триггерная ячейка на ключевых усилителях

Такое состояние триггера устойчивое и может продолжаться неограниченно долго. Справедливо и обратное утверждение: на выходе D1 низкое напряжение, а на выходе D2 – высокое. Переход триггера из одного состояния в другое (переброс, переключение, опрокидывание, запись информации) происходит только под действием входных сигналов х1, х2, подаваемых на дополнительные входы каскадов D1 и D2.

В интегральном исполнении простейшие триггерные ячейки выполняются на логических элементах И-НЕ, ИЛИ-НЕ.

15.2 Классификация триггеров

Классифицировать триггеры можно по способу приема информации, принципу построения и по функциональным возможностям.

По способу приема информации триггеры делятся на асинхронные и синхронные. Асинхронные триггеры воспринимают управляющие, информационные сигналы в момент их поступления на вход триггера и реагируют на них вплоть до момента их снятия. Синхронные триггеры реагируют на установленные информационные сигналы лишь при наличии специального тактирующего сигнала на управляющем входе С (вход синхронизации). Синхронные триггеры со статическим управлением принимают информационные сигналы при подаче на вход С уровня лог.1 (прямой С-вход) или уровня лог. 0 (инверсный С-вход). Триггеры с динамическим управлением воспринимают информационные сигналы в момент перехода тактирующего сигнала на входе С из 0 в 1(0/1) или из 1 в 0 (1/0).

По принципу построения триггеры со статическим управлением можно разделить на одноступенчатые и двухступенчатые. Одноступенчатые триггеры имеют в своем составе одну ступень запоминания информации (одну элементарную триггерную ячейку) и схему управления. Двухступенчатые триггеры имеют две последовательно включенные запоминающие ячейки, запись информации вначале производится в первую ячейку (ступень), а затем переписывается во вторую (выходную) ступень.

По функциональным возможностям различаются:

– триггеры с раздельным управлением по входам R и S (RS-триггеры);

– триггеры с приемом информации по входу D (D-триггеры);

– триггеры со счетным входом (T-триггеры);

– универсальные триггеры с информационными входами J и K (JK-триггеры).

Обозначения и назначения входов триггеров:

R (от англ. Reset) – раздельный вход установки в состояние 0 (сброс);

S (от англ. Set) – раздельный вход установки в состояние 1 (включение);

К (от англ. Kill) – внезапное отключение, управление нулем;

J (от англ. Jerk) – внезапное включение, управление единицей;

Т – счетный вход;

D (от англ. Delay – задержка, Data – данные) – информационный вход установки триггера в состояние, соответствующее логическому уровню на этом входе;

С (от англ. Clock) – исполнительный, управляющий (синхронизирующий) вход, вход тактовых импульсов;

V – разрешающий управляющий вход.

Основными техническими характеристиками триггера являются: быстродействие, потребляемая мощность, напряжение питания, помехоустойчивость, уровни входных и выходных сигналов, функциональные возможности.

Для обозначения функциональных возможностей триггеров в интегральном исполнении используется следующая маркировка: TR – RS-триггер, TB – JK-триггер, TM – D-триггер.

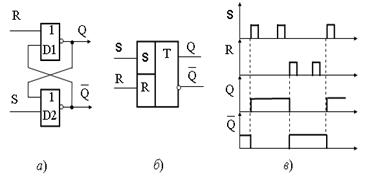

15.3 Триггерная ячейка R-S -типа

Простейшая триггерная ячйка представляет собой симметричную структуру из двух логических элементов ИЛИ-НЕ либо И-НЕ, охваченных положительной обратной связью. Схема симметричного триггера на логических элементах ИЛИ-НЕ, его условное обозначение и временные диаграммы работы приведены на рисунке 15.2.Чтобы понять работу триггера, обратимся к таблице истинности логического элемента ИЛИ-НЕ, приведенной в таблице 15.1. Из анализа таблицы можно заключить, что наличие лог.1на одном из ее входов обязательно приводит к появлению лог.0 на выходе, независимо от уровней сигналов на других входах. Поэтому уровень лог.1 является активным для логической ячейки ИЛИ-НЕ. Уровень, обратный активному (лог.0), называется пассивным.

Рисунок 15.2 − Асинхронный RS-триггер на элементах ИЛИ-НЕ: а − логическая структура; б − условное изображение; в − временные диаграммы

Следовательно, в пассивном состоянии (режим хранения ранее полученной информации) на управляющих входах S и R должен быть лог.0. На одном из выходов триггера будет лог.1, а на противоположном – лог.0. Одному из выходов триггера присваивают наименование прямого (в силу симметрии – любому) и обозначают буквой Q (ку), а другому – инверсного и обозначают  (не ку). О содержании информации, записанной в триггер, судят только по логическому уровню на прямом выходе. Переключение триггера из одного состояния в другое происходит при поочередной подаче управляющих сигналов на его входы. Если при подаче на один из входов триггера лог. 1 (на другом входе при этом присутствует низкий уровень напряжения) на прямом выходе Q триггера установится лог. 0, то этому входу присваивается название R, а противоположный вход называют S. Пусть на выходе триггера Q, было единичное напряжение (триггер включен) и на вход R ячейки D1 подали лог.1. Тогда на входе ячейки D1 действует логическая сумма сигналов R и

(не ку). О содержании информации, записанной в триггер, судят только по логическому уровню на прямом выходе. Переключение триггера из одного состояния в другое происходит при поочередной подаче управляющих сигналов на его входы. Если при подаче на один из входов триггера лог. 1 (на другом входе при этом присутствует низкий уровень напряжения) на прямом выходе Q триггера установится лог. 0, то этому входу присваивается название R, а противоположный вход называют S. Пусть на выходе триггера Q, было единичное напряжение (триггер включен) и на вход R ячейки D1 подали лог.1. Тогда на входе ячейки D1 действует логическая сумма сигналов R и  причем R

причем R

=1

=1  0 = 1. В результате входного воздействия на выходе Q установится лог.0 (триггер выключен). Теперь на входах ячейки D2 действует два логических нуля (S

0 = 1. В результате входного воздействия на выходе Q установится лог.0 (триггер выключен). Теперь на входах ячейки D2 действует два логических нуля (S  Q = 0

Q = 0  0 = 0) и на выходе

0 = 0) и на выходе  установится лог.1. Новое состояние устойчивое, оно сохраняется даже при снятии управляющего сигнала R, т.к. R Ú

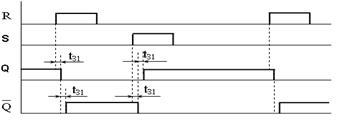

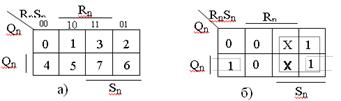

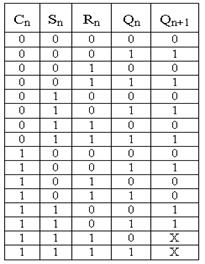

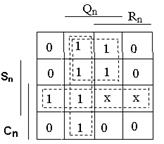

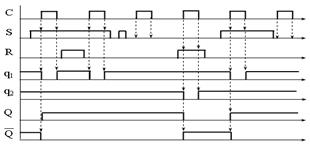

установится лог.1. Новое состояние устойчивое, оно сохраняется даже при снятии управляющего сигнала R, т.к. R Ú  = 0 Ú 1 = 1. Аналогичным образом происходит переключение под действием сигнала S. Триггер сохраняет предыдущее состояние при подаче активного уровня R на ранее выключенный триггер или сигнала S на включенный триггер. При одновременной подаче сигналов S = R = 1 на выходах ячеек D1 и D2 установится уровень логического нуля и после одновременного снятия этих сигналов триггер по случайному закону перейдет в состояние «включен» либо «выключен», т.е. его состояние однозначно не определено, что обозначается знаками: н /о, Φ, ∞, *, X. Описание функционирования RS-триггера можно представить в виде полной таблицы переходов (таблица 15.2). Исходное состояние указывается для такта tn, а выходная функция для такта tn+1. Временные диаграммы переключения RS-триггера с учетом среднего времени задержки распространения tЗ1 сигнала при передаче через логический элемент приведены на рисунке 15.3. Предположим, что в исходном состоянии на прямом выходе Q элемента D1 (рисунок 15.3) установлена лог. 1. Подадим на вход R короткий сигнал установки «нуля». При достижении входным напряжением некоторого порогового значения начинается спад выходного напряжения на выходе D1. По цепи обратной связи спадающее напряжение с выхода Q поступает на один из входов логической ячейки D2, на втором входе которой S = 0. В определенный момент начинается запирание ячейки D2, через tЗ1 оно заканчивается; формируется фронт выходного импульса

= 0 Ú 1 = 1. Аналогичным образом происходит переключение под действием сигнала S. Триггер сохраняет предыдущее состояние при подаче активного уровня R на ранее выключенный триггер или сигнала S на включенный триггер. При одновременной подаче сигналов S = R = 1 на выходах ячеек D1 и D2 установится уровень логического нуля и после одновременного снятия этих сигналов триггер по случайному закону перейдет в состояние «включен» либо «выключен», т.е. его состояние однозначно не определено, что обозначается знаками: н /о, Φ, ∞, *, X. Описание функционирования RS-триггера можно представить в виде полной таблицы переходов (таблица 15.2). Исходное состояние указывается для такта tn, а выходная функция для такта tn+1. Временные диаграммы переключения RS-триггера с учетом среднего времени задержки распространения tЗ1 сигнала при передаче через логический элемент приведены на рисунке 15.3. Предположим, что в исходном состоянии на прямом выходе Q элемента D1 (рисунок 15.3) установлена лог. 1. Подадим на вход R короткий сигнал установки «нуля». При достижении входным напряжением некоторого порогового значения начинается спад выходного напряжения на выходе D1. По цепи обратной связи спадающее напряжение с выхода Q поступает на один из входов логической ячейки D2, на втором входе которой S = 0. В определенный момент начинается запирание ячейки D2, через tЗ1 оно заканчивается; формируется фронт выходного импульса  . На входе R управляющий сигнал должен удерживаться до окончания переходных процессов, следовательно, его минимальная длительность должна быть: TRMIN ≥ 2tЗ1. В силу симметрии схемы по отношению к сигналу S установки триггера в единичное состоянии можно заключить, что: TSMIN ≥ 2tЗ1. Отсюда следует вывод: минимальный период переключения триггера будет: TMIN = TRMIN + TSMIN ≥ 4tЗ1. Этим результатом следует руководствоваться при практическом использовании асинхронных RS-триггеров. Приведенную выше таблицу функционирования триггера можно записать в минимизированной форме (таблица 15.3.). Из таблицы 15.1 видно, что при наборе R = S = 0 триггер сохраняет свое прежнее состояние. Набор R = 1, S = 0 переводит триггер в нулевое состояние, набор R = 0, S = 1 устанавливает на прямом выходе лог.1. Комбинация S = R = 1 является условно запрещенной, т.к. приводит в итоге к неопределенному результату.Определим характеристическое уравнение, определяющее функционирование R-S триггера. Для этого воспользуемся таблицей 15.2 и картой Карно для трех переменных. На рисунке 15.4, а приведена эталонная карта Карно, а на рисунке 15.4, б карта с нанесенными наборами нулей и единиц из таблицы 15.2.

. На входе R управляющий сигнал должен удерживаться до окончания переходных процессов, следовательно, его минимальная длительность должна быть: TRMIN ≥ 2tЗ1. В силу симметрии схемы по отношению к сигналу S установки триггера в единичное состоянии можно заключить, что: TSMIN ≥ 2tЗ1. Отсюда следует вывод: минимальный период переключения триггера будет: TMIN = TRMIN + TSMIN ≥ 4tЗ1. Этим результатом следует руководствоваться при практическом использовании асинхронных RS-триггеров. Приведенную выше таблицу функционирования триггера можно записать в минимизированной форме (таблица 15.3.). Из таблицы 15.1 видно, что при наборе R = S = 0 триггер сохраняет свое прежнее состояние. Набор R = 1, S = 0 переводит триггер в нулевое состояние, набор R = 0, S = 1 устанавливает на прямом выходе лог.1. Комбинация S = R = 1 является условно запрещенной, т.к. приводит в итоге к неопределенному результату.Определим характеристическое уравнение, определяющее функционирование R-S триггера. Для этого воспользуемся таблицей 15.2 и картой Карно для трех переменных. На рисунке 15.4, а приведена эталонная карта Карно, а на рисунке 15.4, б карта с нанесенными наборами нулей и единиц из таблицы 15.2.

Таблица 15.1

| a | b |

|

| a | b |

|

Таблица 15.2

| Набор | tn | tn+1 | ||

| Rn | Sn | Qn | Qn+1 | |

| X | ||||

Из таблицы видно, что имеется всего лишь три набора (2, 4, 6), на которых Qn+1 принимает единичное значение. На карте получилось два контура, которые дают выражение, описывающее функционирование RS-триггера: Qn+1 = Sn

Qn. Наличие запрещенной комбинации Sn = Rn = 1 требует, чтобы произведение Rn Sn всегда было равно 0.

Qn. Наличие запрещенной комбинации Sn = Rn = 1 требует, чтобы произведение Rn Sn всегда было равно 0.

Рисунок 15.3 - Временные диаграммы работы

Рисунок 15.3 - Временные диаграммы работы

RS-триггера с учетом задержки распространения

Таблица 15.3

| tn | tn+1 | |||

| Набор | Rn | Sn | Qn | Qn+1 |

| Qn | Qn | |||

| Qn | ||||

| Qn | ||||

| Qn | X |

Рисунок 15.4 – Карты Карно RS-триггера:

а − эталонная; б − для Qn+1

15.4 Асинхронные RS-триггеры на логических элементах И-НЕ

Логическая структура и функциональное обозначение RS-триггера, выполненного на логических элементах И-НЕ, приведена на рисунке 15.5. Отличительной особенностью триггера является то, что активными уровнями являются лог. 0, а пассивными лог. 1. Действительно, появление хотя бы одного «0» в логическом произведении приводит к обнулению входной функции и появлению лог. 1 на инвертирующем выходе. Инверсные управляющие входы на функциональной схеме обозначены кружочками, а логические обозначения отмечаются знаками инверсии (  ,

,  ). Причем следует отметить, что если функциональный вход отмечен кружочком (активный уровень «ноль»), то на поле управляющих сигналов функциональной схемы должен быть указаны прямые наименования сигналов (S, R).

). Причем следует отметить, что если функциональный вход отмечен кружочком (активный уровень «ноль»), то на поле управляющих сигналов функциональной схемы должен быть указаны прямые наименования сигналов (S, R).

а − логическая структура; б − функциональное обозначение; в − временные диаграммы

Рисунок 15.5 – Асинхронный SR-триггер на ЛЭ И-НЕ

В режиме хранения информации на входы S и R должна быть подана лог.1 (S = R = 1). Переключение триггера будет происходить при подаче на один из входов лог. 0. Комбинация S = R = 0 считается «запрещенной», т.к. устанавливает на обоих выходах триггера единичное напряжение, после снятия управляющих сигналов состояние триггера неопределено (равновероятно «включен» – «выключен»). Сказанное иллюстрируется таблицей функционирования (таблица 15.4) RS-триггера с инверсным управлением. С помощью карты Карно можно получить характеристическое выражение для описания функционирования триггера: Qn+1 =  n + Rn Qn. Быстродействие данного триггера также будет определяться задержкой распространения на двух логических элементах, равной 2tз1, при поступлении каждого управляющего сигнала.

n + Rn Qn. Быстродействие данного триггера также будет определяться задержкой распространения на двух логических элементах, равной 2tз1, при поступлении каждого управляющего сигнала.

Таблица 15.4 −Минимизированная таблица

истинности для RS-триггера с инверсным

управлением

| tn | tn+1 | |||

| Набор | Rn | Sn | Qn | Qn+1 |

| Qn | X | |||

| Qn | ||||

| Qn | ||||

| Qn | Qn |

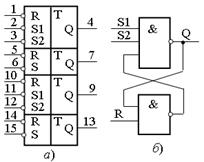

Практическая реализация. Номенклатура RS-триггеров, выпускаемых промышленностью весьма ограниченна. Можно отметить триггеры К555ТР2 серии ТТЛШ и К564ТР2 серии КМОП. Каждая из серий содержит в своем составе по четыре самостоятельных RS-триггера. Условное графическое обозначение и функциональная схема одного триггера приведены на рисунке 15.6.

Рисунок 15.6 – Условное изображение: а − К555ТР2;

б − схема одного триггера

Каждый триггер выполнен на двух логических ячейках И-НЕ, следовательно, активными управляющими уровнями являются логические нули. Для расширения функциональных возможностей два триггера имеют по два входа S, являющихся равноценными.

15.5 Синхронные одноступенчатые триггеры

Синхронные RS-триггеры. Особенностью синхронного RS-триггера является наличие C-входа, на который подаются синхронизирующие (тактирующие) импульсы. Управляющие сигналы R, S могут поступать на управляющие входы элементарной триггерной ячейки только при наличии тактирующего импульса. Логическая схема синхронного RS-триггера приведена на рисунке 15.7, а, а его функциональное обозначение на рисунке 15.7, б.

Собственно триггерная ячейка образована логическими ячейками D3, D4, пунктирными линиями указаны входы асинхронной установки триггера  . Сигналы S и R могут пройти на управляющие входы триггерной ячейки только при условии наличия тактирующего импульса С = 1, при этом

. Сигналы S и R могут пройти на управляющие входы триггерной ячейки только при условии наличия тактирующего импульса С = 1, при этом  и

и  .

.

а − логическая структура; б − функциональное обозначение

Рисунок 15.7 – Синхронный одноступенчатый RS-триггер

Следовательно, одновременная подача управляющих сигналов S = R = 1 «запрещена», поскольку, как и в асинхронном триггере, приводит к неопределенному состоянию. При подаче сигнала S = 1 (R = 0, C = 1) произойдет установка триггерной ячейки в единичное состояние, при R = 1 (S = 0, C = 1) на выходе ячейки установится низкий уровень напряжения. В отсутствие тактирующего импульса (С = 0) триггерная ячейка находится в режиме хранения информации.

Закон функционирования синхронного SR-триггера приведен в таблице 15.5. В таблице 15.6 представлена карта Карно, заполненная в соответствии с таблицей 15.4 функционирования триггера. Используя эту карту, получим минимизированное логическое выражение для описания работы синхронного триггера:

Q n+1 = Rn Qn v Cn Q n v Cn Sn = Qn (Rn v Cn) v Cn Sn.

Таблица 15.5 − Закон функционирования синхронного

RS - трггера

На рисунке 15.8 приведены временные диаграммы работы синхронного RS-триггера, иллюстрирующие описанный процесс. Cудя по рисунку, переключение триггера происходит только при одновременном воздействии на вход триггера управляющего сигнала и тактового импульса. Отсюда можно сделать вывод, что помехоустойчивость синхронного триггера примерно в Q раз больше, чем асинхронного, где Q – скважность импульсов синхронизации.

Таблица 15.6 − Карта Карно

Рисунок 15.8 – Временные диаграммы синхронного

RS-триггера

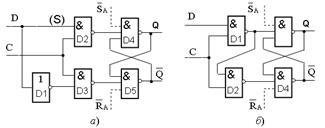

15.6 D-Триггеры

Функциональной особенностью триггера типа D является то, что он с помощью тактирующего импульса фиксирует на выходе Q информацию (0,1), поступившую на вход D в такте n, и запоминает ее до прихода очередного n + 1 синхроимпульса. Для реализации этого способа записи информации необходимо в управляющие цепи синхронного триггера внести некоторые изменения (рисунок 15.9).

Можно сигнал S в прямой форме подавать на вход логической ячейки D2, а в инверсной форме – на вход D3 (рисунок 15.9, а). В этом случае обеспечивается противофазное управление по входам S и R ячеек D2, D3, а вход S получает название D. Второй вариант реализации заключается в том, что инверсное значение сигнала S получают на выходе логической ячейки D1 (рисунок 15.9) и подают в качестве сигнала R на вход ячейки D2.

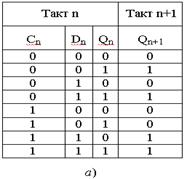

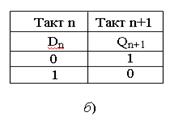

Таблица переходов D-триггера в полной и сокращенной форме представлена в таблице 15.7, а и б соответственно.

В отсутствие тактирующих импульсов триггер находится в режиме хранения ранее полученной информации. С приходом импульса синхронизации происходит запись информации, установленной на входе D. Поскольку D-триггеров без цепей синхронизации не существует, то первые четыре строки таблицы 15.7, а можно исключить, в результате получим сокращенную таблицу состояний (таблица 15.7, б).

Рисунок 15.9 – Логическая структура D-триггера:

а − с дополнительным инвертором на входе; б − с инвертированием на входной логике

Закон функционирования D-триггера запишется в виде: Q n+1 = C n D n или в сокращенной форме: Q n+1 = D n.

Поскольку триггер задерживает на один такт информацию, поданную на вход D в предыдущем такте, то он получил название триггер «задержки». Правильными будут названия: «запоминающий триггер», «триггер памяти», так как он запоминает входную информацию на время очередного такта.

Недостатком статического способа синхронизации является то, что запись информации происходит в течение длительности импульса синхронизации и любое изменение сигнала на входе D в это время приводит к изменению выходного сигнала.

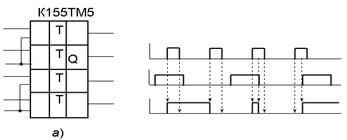

Практическая реализация. Микросхема типа К155ТМ5 представляет собой триггеры со статическим управлением. В каждом корпусе содержится четыре D-триггера с самостоятельными входами и выходами. Функциональная схема и временные диаграммы приведены на рисунке 15.10. Триггеры микросхемы попарно объединены по входам синхронизации, синхронизирующих входов два: по одному на два триггера (рисунок 15.10, а). Запись информации происходит при наличии единичного напряжения на входе С. Если во время действия тактирующего импульса произойдет изменение информации на входе D, то это изменение зафиксируется на выходе (рисунок 15.10, б).

Таблица 15.7 – Закон функционирования D –триггера:

а − полная таблица; б − сокращенная

Рисунок 15.10 – Микросхема К155ТМ5: а − функциональное обозначение; б − эпюры напряжений

Краткие технические параметры микросхемы: потребляемый ток – 53 mА при напряжении питания 5 В, задержка распространения сигнала – не более 30 нс.

Дата добавления: 2020-03-17; просмотров: 1983;