Изучение схемы логического пробника.

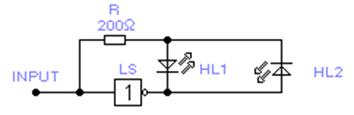

Логический пробник используется для анализа логического состояния входного сигнала. Соберите предложенную на рис. 8.8 схему, выбрав ток срабатывания светодиодов на уровне (1–3) мА.

Рис. 8.8. Схема логического пробника

Пронаблюдайте поведение схемы при свободном входе «INPUT», при поочередной подаче на вход уровня логического нуля (ноль В) и логической единицы (+5 В). Опишите поведение схемы и объясните с указанием возможных путей протекания токов при разных сигналах.

Изучение некоторых свойств и возможных применений полупроводниковых

транзисторов

Биполярные транзисторы характеризуются в статике входной и выходными характеристиками. Входная характеристика определяется вольт-амперной характеристикой перехода база – эмиттер и подобна характеристике диода. Выходные характеристики представляют зависимости коллекторного тока от напряжения коллектор – эмиттер при разных постоянных значениях тока базы. Выходные характеристики учитывают тот факт, что биполярные транзисторы усиливают ток, т.е. характеризуются коэффициентом усиления или передачи (в зависимости от способа включения) тока. В схеме с общим эмиттером транзистор характеризуют интегральным (β) и дифференциальным (h21э) коэффициентами усиления по току. Интегральный определяется отношением коллекторного тока Iк к току базы Iб: β = Iк / Iб. Дифференциальный коэффициент определяется отношением приращений этих токов при выбранном начальном положении рабочей точки:

h21э= ∆Iк / ∆Iб ≈ β»1.

В динамике в схеме с общим эмиттером биполярные транзисторы характеризуют постоянной времени τβ, что соответствует граничной частоте усиления ωβ = 1/τβ, на которой коэффициент уменьшается до 70 % от значения на нулевой частоте.

Полевые транзисторы обладают чрезвычайно высоким входным сопротивлением затвора (управляющий электрод) и характеризуются крутизной характеристики S(мА/В), т.е. зависимостью приращения тока стока ∆Iс от приращения напряжения на затворе относительно истока ∆Uзи: S = ∆Iс / ∆Uзи. Поэтому выходные характеристики полевого транзистора определяются набором зависимостей тока стока от напряжения сток – исток при разных постоянных напряжениях на затворе относительно истока.

Рассмотрим несколько вариантов схемных решений усилительных каскадов на биполярных транзисторах.

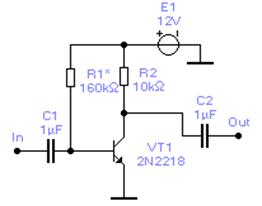

На рис. 9.1 предложен усилительный каскад, выполненный по схеме с общим эмиттером.

Рис. 9.1. Каскад усиления, выполненный по схеме

с общим эмиттером

Каскад предназначен для усиления сигнала переменного тока, поскольку разделительные конденсаторы исключают постоянную составляющую сигнала. Если при заданном напряжении питания E1 определено сопротивление резистора в коллекторе R2 (например, задано) и известно начальное напряжение на коллекторе Uкэ= (постоянная составляющая напряжения), то легко рассчитать начальный коллекторный ток Iк= из выражения

Iк= = (E1 – Uкэ=)/R2.

Зная коэффициент усиления тока в схеме с общим эмиттером (b), легко рассчитать сопротивление резистора R1, которое гарантирует выбранный режим работы каскада по постоянному току:

R1= (E1 – Uбэ=) / Iб=,

Iб== Iк= /b.

Начальное напряжение на коллекторе Uкэ= можно задать равным E1/2, что позволит на выходе получить неискаженный сигнал с максимальной амплитудой.

Каскад усиливает сигнал по напряжению и току. Часто представляет интерес коэффициент усиления каскада по напряжению, который может быть оценен из выражения

ku= (R2h21э)/ h11э,

где h11э – входное дифференциальное сопротивление транзистора в схеме с общим эмиттером, h21э» b – коэффициент усиления по току.

Недостатком каскада является высокая чувствительность к параметрам транзистора и сопротивлению резистора R1. Обычно предполагается подстройка сопротивления резистора в процессе настройки схемы под выбранный транзистор. Незначительные изменения коэффициента усиления транзистора при его замене или при изменении температуры приводят к существенным изменениям начального напряжения на коллекторе, к изменению положения рабочей точки. Чтобы существенно снизить нестабильность положения рабочей точки при изменении параметров деталей, используют цепи стабилизации положения рабочей точки, которые предполагают применение отрицательной обратной связи. Обратнаясвязь – подачавыходногосигналаусилителяиличастиэтогосигналанавход.Обратнаясвязьотрицательная,еслионаприводиткуменьшениюкоэффициентаусилениявсейсхемы.Для стабилизации положения рабочей точки можно ограничиться применением отрицательной обратной связи по постоянному току. Тогда на переменном токе сохраняется высокий коэффициент усиления сигнала.

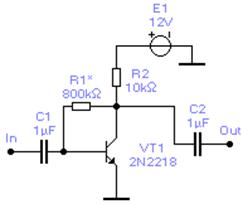

На рис. 9.2 предложено возможное схемное решение каскада со стабилизацией положения рабочей точки.

Рис. 9.2. Каскад со стабилизацией положения рабочей точки

По постоянному току справедлива система из двух уравнений:

IR2= Iб=+ Iк=,

Iб== Iк= /b,

где IR2 – ток через резистор R2.

Эти равенства позволяют рассчитать при необходимости недостающие параметры схемы или входящих в схему компонентов. Например, если известен коэффициент усиления транзистора по току b и сопротивление коллекторного резистора R2 или ток через него, то, задав требуемое значение начального напряжения на коллекторе, легко рассчитать сопротивление в базовой цепи R1. Легко рассчитать и величину смещения положения рабочей точки каскада (напряжения на коллекторе) при изменении параметров деталей схемы.

Поскольку резистор обратной связи R1 создает отрицательную обратную связь, которая действует на любой частоте, то коэффициент усиления этого каскада при одинаковых условиях с предыдущей схемой окажется ниже.

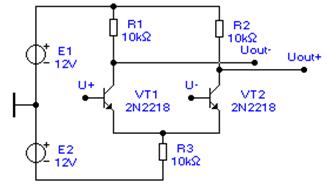

Широкое применение, особенно в составе операционных усилителей, находят так называемые дифференциальные или балансные каскады (рис. 9.3). Особенностями этих каскадов являются невысокий дрейф нуля благодаря симметрии и взаимной компенсации изменений параметров транзисторов, наличие прямого и инвертирующего входов (дифференциальный вход) и наличие двух выходов (дифференциальный выход). Входные сигналы U+ и U– формируются относительно потенциала общего провода. Каскад усиливает только разностный сигнал. Выходной дифференциальный сигнал каскада равен

Uвых=Uout+ – Uout– = ku(U+ – U–),

где ku= (R2 × h21э) / h11э – коэффициент усиления каскада при условии R1= R2.

Рис. 9.3. Дифференциальный каскад

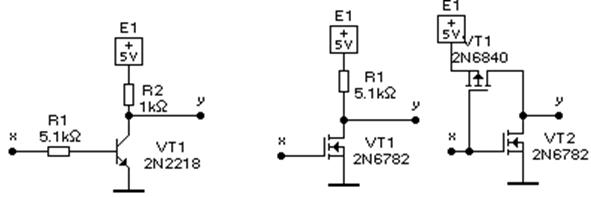

В основу практически каждого современного логического элемента положен транзисторный ключ, который, с одной стороны, выполняет функцию усиления мощности сигнала, а с другой – реализует логическую функцию НЕ (отрицание). Простейшие схемные решения транзисторных ключей предложены на рис. 9.4.

а) б) в)

Рис. 9.4. Схемные решения транзисторных ключей

Все предложенные решения реализуют функцию «отрицание», т.е. являются инверторами, элементами, инвертирующими состояние входного сигнала x. Выходная функция y для них равна  .

.

В предложенном на рис. 9.4,а транзисторном ключе резистор R1 используется для ограничения базового тока, а резистор R2 является коллекторной нагрузкой транзистора и позволяет по величине выходного напряжения определить одно из крайних состояний транзистора: открыт транзистор или закрыт. При высоком уровне на входе транзистор открыт и формирует на выходе близкий к нулю потенциал. Если же на входе нуль, то транзистор закрыт и на выходе формируется единица. Недостатком данного ключа является возможность перехода транзистора в режим насыщения при открывании, что приводит к потере быстродействия.

В предложенных на рис. 9.4,б,в транзисторных ключах используются МДП- или МОП-транзисторы с индуцированными каналами (полевые транзисторы). Применение в стоковой цепи транзисторного ключа, предложенного на рис. 9.4,б, резистора существенно уменьшает быстродействие (сопротивление резистора обычно велико) и нагрузочную способность. При открытом транзисторе подобный элемент потребляет ток от источника, что является недостатком как данного элемента, так и элемента на биполярном транзисторе, схема которого предложена на рис. 9.4,а. Поэтому в настоящее время находят все большее применение транзисторные ключи и логические элементы, выполненные с использованием взаимодополняющих, или комплементарных, МДП-транзисторов, т.е. транзисторов с разными каналами проводимости (см. рис. 9.4,в). О таких элементах говорят, что они выполнены по КМДП-технологии. Транзистор VT1 в схеме рис. 9.4,в имеет p-канал проводимости, а VT2имеет n-канал проводимости. При нулевом потенциале на входе транзистор VT1 оказывается открыт, а VT2 – закрыт. На выходе формируется напряжение величиной E1. При уровне логической единицы (+E1) на входе VT1 закрывается, а VT2 открывается, что приводит к нулю на выходе. Заметим, что сквозной ток через транзисторы VT1 и VT2 в статике не течет, элемент потребляет энергию только в моменты переключения. Выполненный по КМДП- технологии элемент оказывается чрезвычайно экономичным, с высокой нагрузочной способностью и достаточно высоким быстродействием.

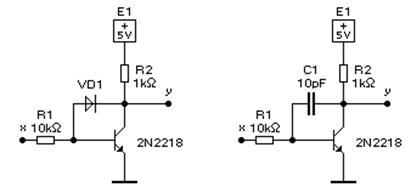

Для повышения быстродействия ключа на биполярном транзисторе используется диод Шотки в цепи нелинейной отрицательной обратной связи. Включение диода показано на рис. 9.5,а. Диод Шотки имеет небольшое прямое падение напряжения (примерно 0,4 В), что позволяет практически исключить насыщение транзистора при включении. Следовательно, при выключении ключа значительно уменьшится время выхода транзистора из насыщения, что приведет к повышению быстродействия.

а) б)

Рис. 9.5. Схема включения диода Шотки VD1 (а) и эквивалентная схема включения паразитной емкости коллекторного перехода C1 (б)

Быстродействие транзисторного ключа в большой степени зависит и от величины паразитной емкости коллекторного перехода C1, которая оказывается включена между базой, т.е. входом схемы, и коллектором, т.е. выходом элемента (показано на рис. 9.5,б). Этот конденсатор оказывается элементом отрицательной обратной связи и уменьшает влияние входного сигнала на транзистор. Его влияние равносильно влиянию конденсатора с емкостью bC1, где b – коэффициент усиления базового тока транзистором в схеме с общим эмиттером.

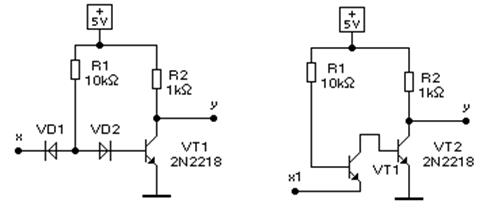

На рис. 9.6 предложены схемные решения простых инверторов, выполненные по технологии ДТЛ и ТТЛ. Применение вместо диодов транзистора в схеме рис. 9.6,б позволяет существенно повысить быстродействие при выключении транзистора, что объясняется обеспечением низкоомной цепи рассасывания накопленного в базе заряда через открытый транзистор VT1.

|

а) б)

Рис. 9.6. Реализация простых инверторов в ДТЛ (а) и ТТЛ (б)

Дата добавления: 2021-12-14; просмотров: 91;